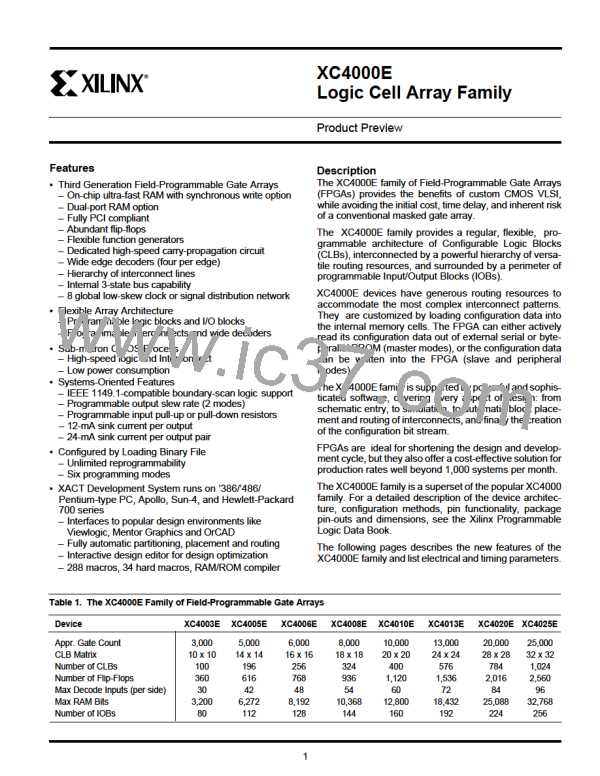

IOB Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%

functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing

patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more

precise, and more up-to-date timing information, use the values provided by the XACT timing calculator and used in the simulator.

Speed Grade

-4

-3

-2

Description

Symbol Min Max

Min Max Min Max Units

Input

Propagation Delays

Pad to I1, I2

TPID

TPLI

TPDLI

TIKRI

TIKLI

2.5

3.6

7.1

2.8

3.0

ns

ns

ns

ns

ns

Pad to I1, I2, via transparent latch (no delay)

Pad to I1, I2, via transparent latch (with delay)

Clock (IK) toI1, I2, (flip-flop)

Clock (IK) to I1, I2 (latch enable, active Low)

Set-up Time (Note 3)

Pad to Clock (IK), no delay

Pad to Clock (IK) with delay

TPICK

TPICKD

4.7

8.3

ns

ns

Hold Time (Note 3)

Pad to Clock (IK), no delay

Pad to Clock (IK) with delay

TIKPI

TIKPID

0

0

ns

ns

Output

Propagation Delays

Clock (OK) to Pad

same

Output (O) to Pad

same

3-state to Pad begin hi-Z (slew-rate independent)

3-state to Pad active and valid (fast)

(fast)

(slew rate limited)

(fast)

TOKPOF

TOKPOS

TOPF

4.6

11.2

5.8

12.4

4.2

ns

ns

ns

ns

ns

ns

ns

(slew-rate limited)

TOPS

TTSHZ

TTSONF

TTSONS

8.1

14.7

same

(slew -rate limited)

Set-up and Hold Times

Output (O) to clock (OK) set-up time

Output (O) to clock (OK) hold time

TOOK

TOKO

3.7

0

ns

ns

Clock

Clock High or Low time

TCH/TCL

4.0

ns

Global Set/Reset

Delay from GSR net through Q to I1, I2

Delay from GSR net to Pad

GSR width*

TRRI

TRPO

TMRW

7.2

ns

ns

ns

18.9

* Timing is based on the XC4005E. For other devices see XACT timing calculator.

** See preceding page

Notes: 1. Timing is measured at pin threshold, with 50 pF external capacitive loads (incl. test fixture). Slew rate limited output

rise/fall times are approximately two times longer than fast output rise/fall times. For the effect of capacitive loads on

ground bounce, see pages 8-8 through 8-10.

2. Voltage levels of unused (bonded and unbonded) pads must be valid logic levels. Each can be configured with the

internal pull-up or pull-down resistor or alternatively configured as a driven output or be driven from an external source.

3. Input pad setup times and hold times are specified with respect to the internal clock (IK). To calculate system setup time,

subtract clock delay (clock pad to IK) from the specified input pad setup time value, but do not subtract below zero.

Negative hold time means that the delay in the input data is adequate for the external system hold time to be zero,

provided the input clock uses the Global signal distribution from pad to IK.

3

XILINX [ XILINX, INC ]

XILINX [ XILINX, INC ]