X4043/45

TIMING DIAGRAMS

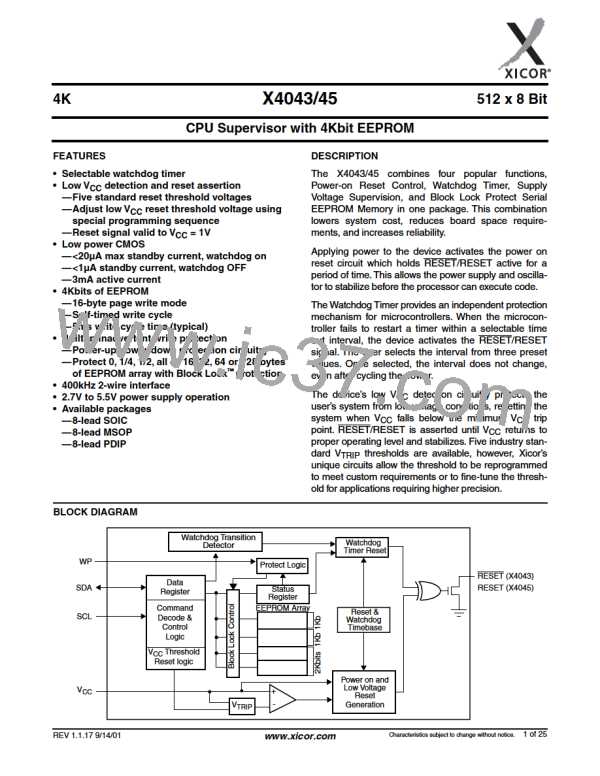

Bus Timing

t

t

t

t

R

F

HIGH

LOW

SCL

t

SU:DAT

t

t

t

SU:STO

SU:STA

HD:DAT

t

HD:STA

SDA IN

t

t

t

BUF

AA

DH

SDA OUT

WP Pin Timing

START

SCL

Clk 1

Clk 9

Slave Address Byte

SDA IN

WP

t

t

HD:WP

SU:WP

Write Cycle Timing

SCL

SDA

8th Bit of Last Byte

ACK

t

WC

Stop

Condition

Start

Condition

Nonvolatile Write Cycle Timing

Symbol

Parameter

Write cycle time

Min.

Typ.(7)

Max.

Unit

(7)

t

5

10

ms

WC

Notes: (7) t

is the time from a valid stop condition at the end of a write sequence to the end of the self-timed internal nonvolatile write cycle.

WC

It is the minimum cycle time to be allowed for any nonvolatile write by the user, unless acknowledge polling is used.

Characteristics subject to change without notice. 16 of 25

REV 1.1.17 9/14/01

www.xicor.com

XICOR [ XICOR INC. ]

XICOR [ XICOR INC. ]