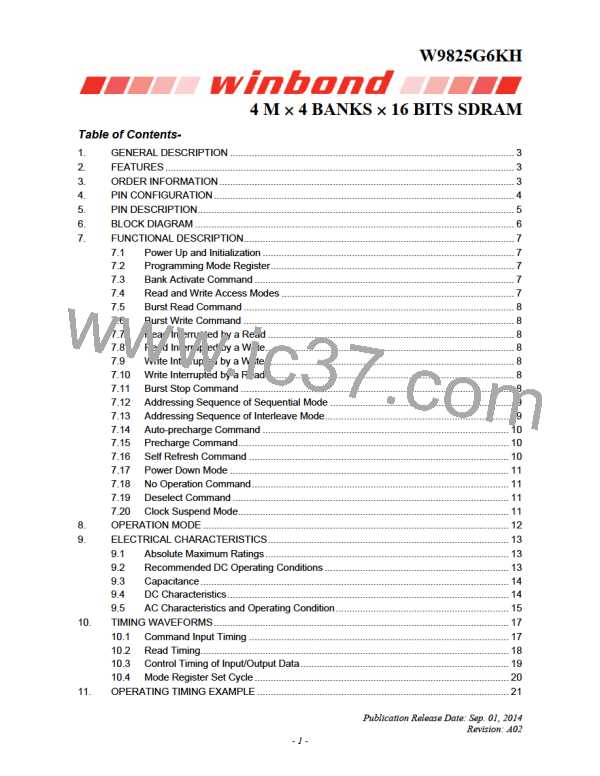

W9825G6KH

11.19 Timing Chart of Burst Stop Cycle (Burst Stop Command)

0

1

2

3

4

5

6

7

8

9

10

11

(1) Read cycle

( a ) CAS latency =2

Command

Read

BST

Q3

DQ

Q0

Q1

Q0

Q2

Q1

Q4

Q3

( b )CAS latency =

3

Command

Read

BST

Q2

DQ

Q4

(2) Write cycle

Command

Write

Q0

BST

DQ

Q1

Q2

Q3

Q4

Note: BST

represents the Burst stop command

11.20 Timing Chart of Burst Stop Cycle (Precharge Command)

0

1

2

3

4

5

6

7

8

9

10

11

(1) Read cycle

(a) CAS latency =2

Command

Read

Read

PRCG

Q3

DQ

Q0

Q1

Q0

Q2

Q1

Q4

Q3

(b) CAS latency =3

Command

PRCG

Q2

DQ

Q4

(2) Write cycle

Write

Q0

PRCG

Command

tWR

DQM

DQ

Q1

Q2

Q3

Q4

Publication Release Date: Sep. 01, 2014

Revision: A02

- 38 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]