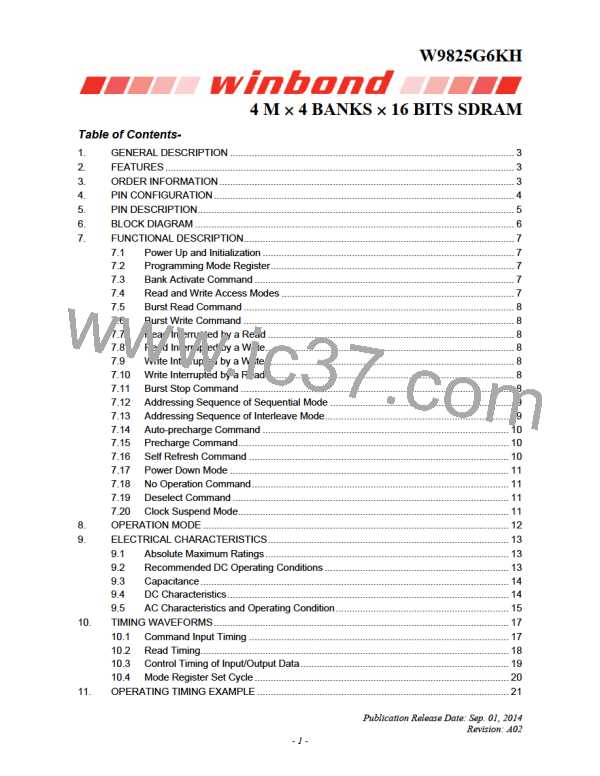

W9825G6KH

11.17 Timing Chart of Read to Write Cycle

In the case of Burst Length = 4

1

2

3

4

5

6

7

8

9

10

11

0

(1) CAS Latency=2

(

a ) Command

Read Write

DQM

DQ

D0

D1

D2

D3

(

b

) Command

DQM

Read

Write

D0

D1

D2

D2

D3

D3

DQ

(2) CAS Latency=3

(

a ) Command

Read Write

DQM

DQ

D0

D1

(

b

) Command

DQM

Read

Write

D0

D1

D2

D3

DQ

Note: The Output data must be masked by DQM to avoid I/O conflict.

11.18 Timing Chart of Write to Read Cycle

In the case of Burst Length=4

1

2

3

4

5

6

7

8

9

10

11

0

(1) CAS Latency=2

Write Read

(a )Command

DQM

DQ

D0

Q0

Q1

Q0

Q2

Q1

Q3

Q2

(b)Command

DQM

Read

Write

DQ

D0

D1

Q3

(2) CAS Latency=3

(a )Command

DQM

Write Read

DQ

D0

Q0

Q1

Q0

Q2

Q1

Q3

Q2

(b)Command

DQM

Write

Read

DQ

D0

D1

Q3

Publication Release Date: Sep. 01, 2014

Revision: A02

- 37 -

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]