I5216 SERIES

Advanced Information

PRELIMINARY

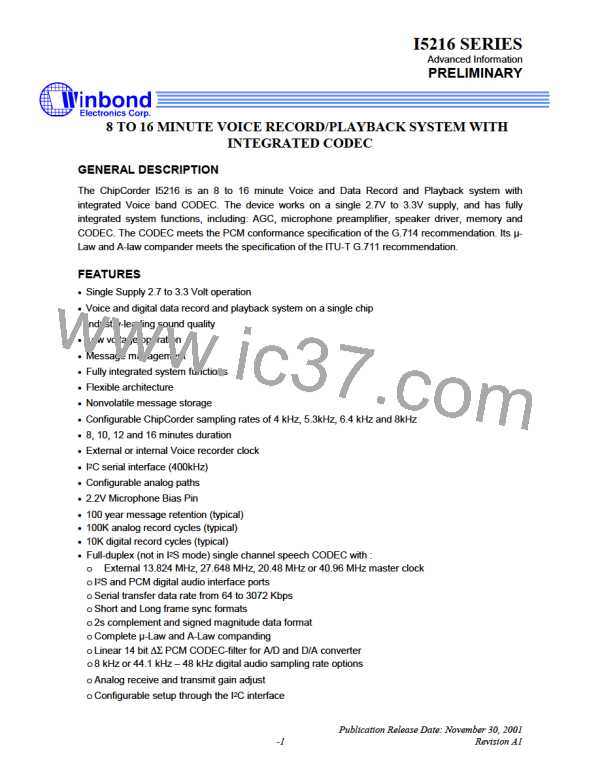

I5216 CODEC DIAGRAM

14 bit

DAO

14 bit

Digital

Σ∆

Demodulator

1 bit D/A

& SC

Digital

Smoothing

Interpolation Filter

µ/A-Law

Expander

or linear

1 bit

ANALOG OUT

Filter

1

MUTE

LAW0

LAW1

(

)

1

3

COG0

COG1

COG2

2

( )

( )

(DAPD)

Anti

Aliasing

Filter

Analog

Σ∆

Modulator

1 bit

SC

AMP

ANALOG IN

CIG0

CIG1

CIG2

(ADPD)

1

(

)

3

15 bit

Digital

Digital

Sample frequency

14 bit

Anti-Aliasing

High pass

Filter

Decimation Filter

HPF0

MUTE

µ/A-Law

Compressor

or linear

(

)

1 1

2

(

)

HSR0

Digital

PLL

LAW0

LAW1

HSR0

(

)

( )

8 bits or 16

bits

CKD2

(

)

÷2

WS

8 bits or 16

bits

I2S0

)

(

PCM / I2S Interface

MCLK

WS SCK SDIO SDI

5/8/01

Publication Release Date: November 30, 2001

Revision A1

-7

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]