I5216 SERIES

Advanced Information

PRELIMINARY

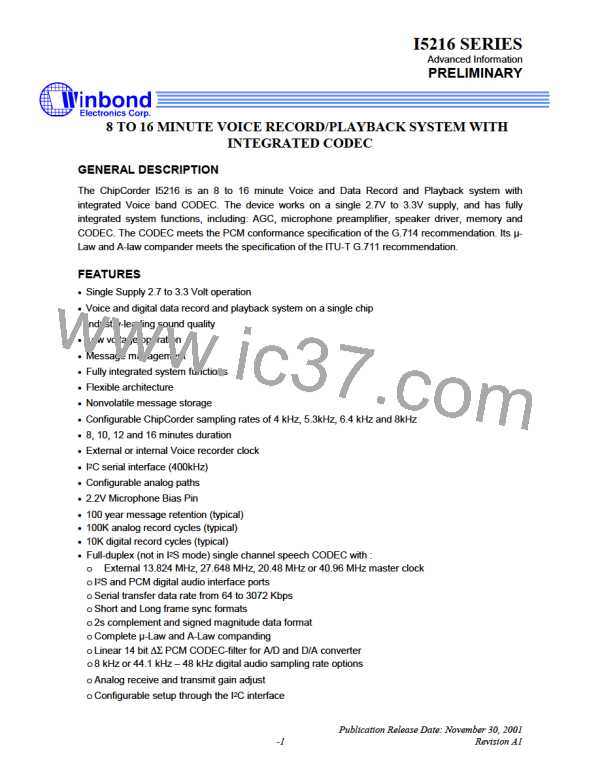

BLOCK DIAGRAMS

I5216 Block Diagram

2.2V Voltage

reference

MICBS

1

MICROPHONE

MIC+

(AGPD)

SUM1

Summing

AMP

SUM1

INP

SUM2

Summing

AMP

MIC IN

FILTO

AGC

SUM1 MUX

Low Pass

Filter

Auto mute

Auto gain

Σ

SUM1

ARRAY

MIC -

1

AUX IN

Σ

(AGPD)

S1M0

S1M1

2

1

1

(FLPD)

(AMT0)

(

)

(FLS0)

1

S2M0

S2M1

AGCCAP

(

)

2

AUX IN

FILTO

ARRAY

1

(INS0)

Internal

Clock

AUX IN

AMP

Multilevel

AUX IN

MCLK

Storage Array

1

DAO

OSPD

CKDV

(AXPD)

FLD0

2

(

)

2

(

)

FLD1

AUX

OUT

AMP

AXG0

AXG1

SUM2

(ANALOG)

2

FILTO

SUM2

(

)

2

AUX OUT

Array I/O Mux

S1S0

S1S1

2 x 64 S/H

(

)

÷2

A/D

CTRL

(DIGITAL)

Program/Read Control

SPEAKER

SP+

(CKD2)

MIC+

MIC-

1

VOL

DAO

2 x 64-bit reg.

ARRAY OUT

(ANALOG)

ARRAY OUT

(DIGITAL)

Spkr.

AMP

INP

SUM2

SP-

2

SUM1

INP

2

OPS0

OPS1

Volume

Control

(

)

OPA0

OPA1

C

CODE

Mux

VOL0

(

)

VOL1

( )

VOL2

DAO

(VLPD)

CDI0

3

1

2

SUM2

(CDI1)

VLS0

VLS1

(

)

2

µ-Law / A-Law /

Linear 14 bit

CODEC

ADPD

DAPD

2

(

)

Power Conditioning

PCM / I2S Interface

SCK SDIO SDI

Device Control

SDA

INT

RAC

A0

A1

SCL

VCCD

VCCA VSSA VSSA VSSD

VCCD

VSSD

WS

5/22/01

Publication Release Date: November 30, 2001

Revision A1

-6

WINBOND [ WINBOND ]

WINBOND [ WINBOND ]