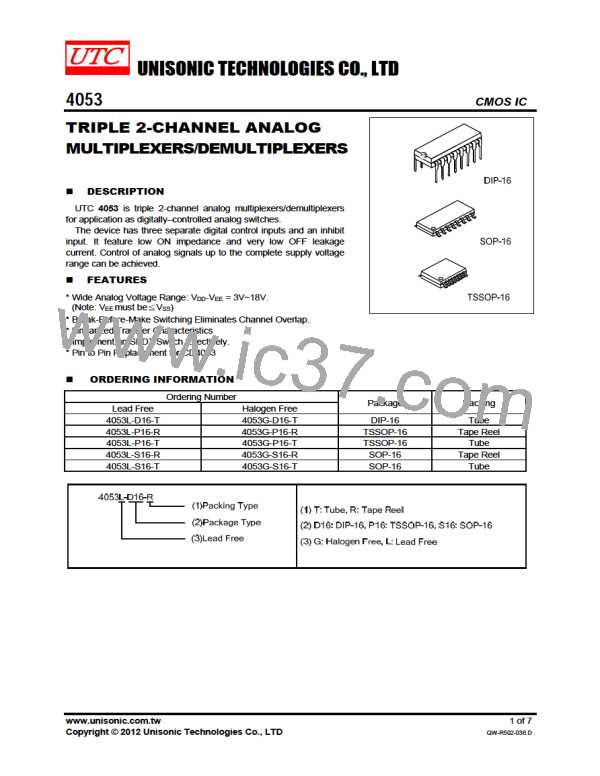

4053

CMOS IC

TEST CIRCUIT

VDD

VDD

VDD

IN/OUT

OUT/IN

VEE

VDD

LEVEL

CONVERTED

OUT/IN

IN/OUT

CONTROL

CONTROL

VEE

Switch Circuit Schematic

TRUTH TABLE

16

VDD

Control Inputs

Select

ON Switches

INH

A 11

B 10

6

BINARY TO 1 - OF - 2

DECODER WITH

INHIBIT

LEVEL

CONVERTER

INHIBIT

C

B

A

UTC 4053

C

9

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

1

Z0 Y0

Z0 Y0

Z0 Y1

Z0 Y1

X0

X1

X0

X1

7

8

VEE

VSS

X0 12

X1 13

14 X

15 Y

0

0

0

0

1

1

1

1

0

0

1

1

0

1

0

1

Z1 Y0

Z1 Y0

Z1 Y1

Z1 Y1

X0

X1

X0

X1

Y0

2

Y1

Z0

1

5

1

x

x

x

None

4

Z

Z1

3

x = Don’t Care

UTC 4053 Functional Diagram

UNISONIC TECHNOLOGIES CO., LTD

5 of 7

QW-R502-036.D

www.unisonic.com.tw

UTC [ Unisonic Technologies ]

UTC [ Unisonic Technologies ]