UCC28951

www.ti.com.cn

ZHCSIQ7A –AUGUST 2018 –REVISED DECEMBER 2021

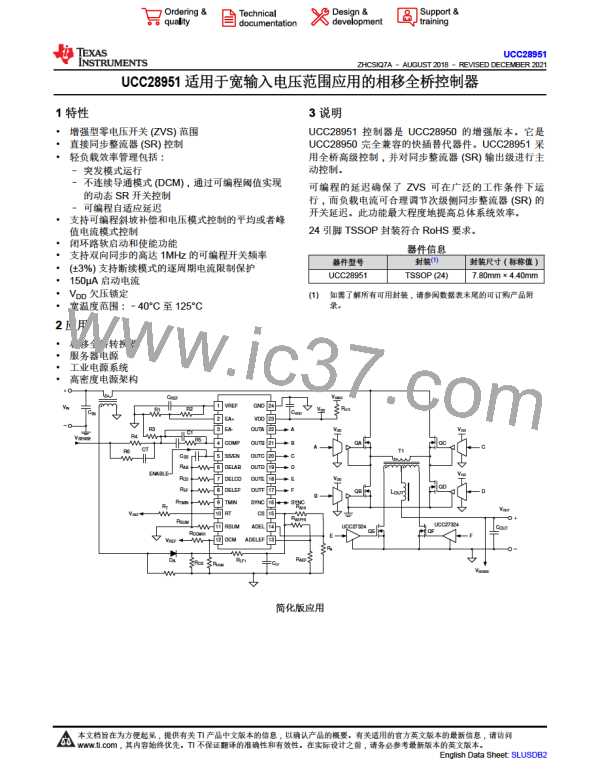

VDD failed and VDD_GOOD goes low,

Everything is shutdown

7.3V rise, 6.7V fall

VDD

VDD_GOOD

4.8V rise, 4.6V fall

VREF

VREF_GOOD

TMIN

CLK

TMIN

Add 0.85V offset to RAMP

COMP

2Vp-p

RAMP

PWM

No PWM pulses shorter than TMIN except

during cycle-by-cycle current limit

A

B

C

D

E

F

No output delay shown, COMP-to-RAMP offset not included.

图6-2. UCC28951 Steady-State and Shutdown Timing Diagram

6.8 Typical Characteristics

7.6

640

7.4

UVLO_RTH

630

620

7.2

7.0

6.8

6.6

6.4

UVLO_HYST

610

600

UVLO_FTH

590

580

6.2

-40

25

TJ - Temperature - °C

125

-40

25

TJ - Temperature - °C

125

图6-3. UVLO Thresholds vs Temperature

图6-4. UVLO Hysteresis vs Temperature

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SLUSDB2

12

Submit Document Feedback

Product Folder Links: UCC28951

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]