UC1842/3/4/5

UC2842/3/4/5

ERROR AMPLIFIER OPEN-LOOP

FREQUENCY RESPONSE

OUTPUT SATURATION CHARACTERISTICS

OPEN-LOOP LABORATORY FIXTURE

High peak currents associated with capacitive loads ne- single point ground. The transistor and 5k potentiometer

cessitate careful grounding techniques. Timing and by- are used to sample the oscillator waveform and apply

pass capacitors should be connected close to pin 5 in a an adjustable ramp to pin 3.

SHUT DOWN TECHNIQUES

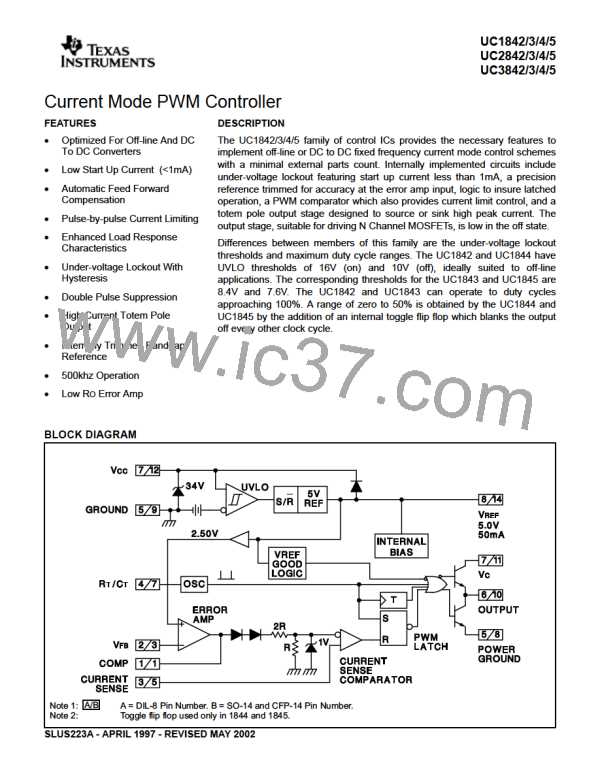

Shutdown of the UC1842 can be accomplished by two clock cycle after the shutdown condition at pin 1 and/or

methods; either raise pin 3 above 1V or pull pin 1 below 3 is removed. In one example, an externally latched

a voltage two diode drops above ground. Either method shutdown may be accomplished by adding an SCR

causes the output of the PWM comparator to be high which will be reset by cycling VCC below the lower

(refer to block diagram). The PWM latch is reset domi- UVLO threshold. At this point the reference turns off, al-

nant so that the output will remain low until the next lowing the SCR to reset.

6

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]