TPS929160-Q1

ZHCSNG0 – APRIL 2023

www.ti.com.cn

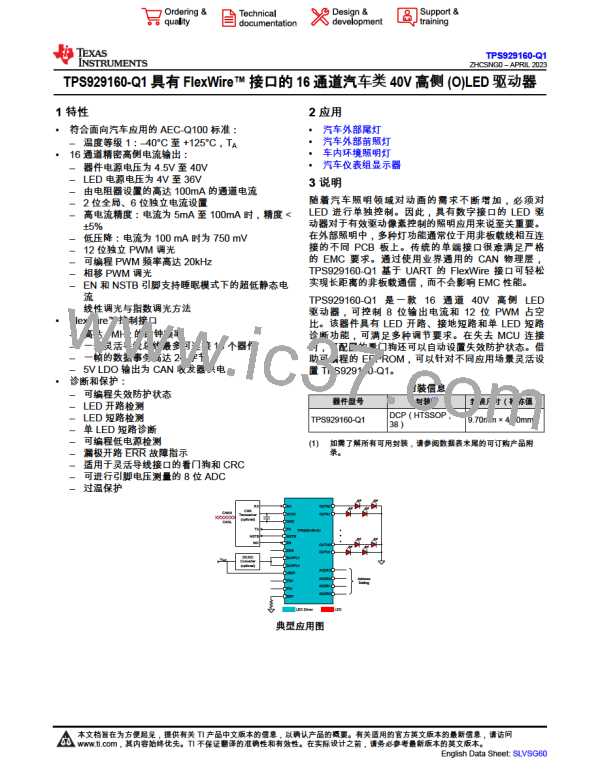

5 Pin Configuration and Functions

RX

VLDO

GND

ADDR3

ADDR2

ADDR1

ADDR0

OUTA0

OUTA1

OUTB0

OUTB1

NC

1

2

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

3

TX

4

NSTB

REF

5

6

7

ERR

8

EN

TPS929160-Q1

DCP

VBAT

SUPPLY

9

OUTC0

OUTC1

NC

10

SUPPLY 11

FS1 12

OUTD0

OUTD1

NC

FS0

OUTH1

OUTH0

13

14

15

OUTE0

OUTG1 16

OUTG0

17

22 OUTE1

21

20 OUTF0

Exposed Pad

NC 18

NC

OUTF1 19

图 5-1. DCP Package 38-Pin HTSSOP with PowerPAD™ Integrated Circuit Package Top View

表 5-1. Pin Functions

PIN

I/O

DESCRIPTION

NO.

1

NAME

RX

I

FlexWire RX

2

VLDO

GND

Power

5-V regulator output

3

̶

Ground

4

TX

O

FlexWire TX

5

NSTB

REF

O

FlexWire NSTB Output

Device current reference setting

Open-drain error indication

Device Enable Pin

6

I/O

7

ERR

I/O

8

EN

I

9

VBAT

SUPPLY

SUPPLY

FS1

Power

Power supply for analog and digital circuit

Power supply for current output channels

Power supply for current output channels

Fail-safe input 1

10

11

12

13

14

15

16

17

18

19

20

Power

Power

I

FS0

I

Fail-safe input 0

OUTH1

OUTH0

OUTG1

OUTG0

NC

O

O

O

O

̶

Current output channel H1

Current output channel H0

Current output channel G1

Current output channel G0

No Connection

OUTF1

OUTF0

O

O

Current output channel F1

Current output channel F0

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: TPS929160-Q1

English Data Sheet: SLVSG60

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]