TPS54332

SLVS875B –JANUARY 2009–REVISED FEBRUARY 2012

www.ti.com

Estimated Circuit Area

The estimated printed circuit board area for the components used in the design of Figure 12 is 0.58 in2. This area

does not include test points or connectors.

ELECTROMAGNETIC INTERFERENCE (EMI) CONSIDERATIONS

As EMI becomes a rising concern in more and more applications, the internal design of the TPS54332 takes

measures to reduce the EMI. The high-side MOSFET gate drive is designed to reduce the PH pin voltage

ringing. The internal IC rails are isolated to decrease the noise sensitivity. A package bond wire scheme is used

to lower the parasitics effects.

To achieve the best EMI performance, external component selection and board layout are equally important.

Follow the Step by Step Design Procedure above to prevent potential EMI issues.

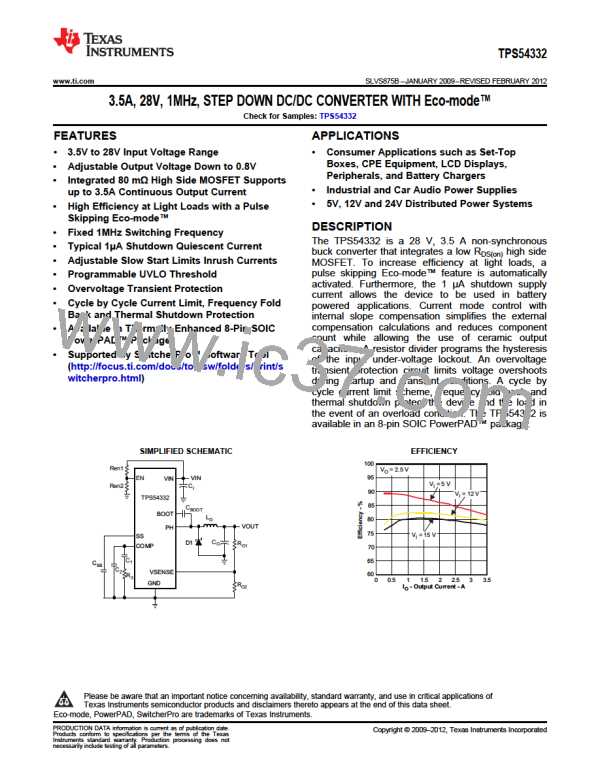

APPLICATION CURVES

100

95

90

85

80

75

70

65

60

100

V

= 2.5 V

V

= 2.5 V

O

O

V = 5 V

I

95

90

85

V = 5 V

I

V = 12 V

I

V = 12 V

V = 15 V

I

I

80

75

V = 15 V

I

70

65

60

55

50

0

0.025 0.05 0.075 0.1 0.125 0.15 0.175 0.2 0.225 0.25

- Output Current - A

0

0.5

1

1.5

2

2.5

3

3.5

I

- Output Current - A

I

O

O

Figure 14. TPS54332 Efficiency

Figure 15. TPS54332 Low Current Efficiency

1

0.9

0.8

0.7

0.6

0.025

0.02

0.015

0.01

V = 15 V

I

0.005

V = 12 V

I

0.5

0.4

0.3

0.2

0.1

I = 1 A

O

0

-0.005

-0.01

V = 5 V

I

-0.015

0

-0.02

-0.1

-0.025

0

0.5

1

1.5

2

2.5

3

3.5

5

6

7

8

9

10

11

12

13

14

15

I

- Output Current - A

O

V - Input Voltage - V

I

Figure 16. TPS54332 Load Regulation

Figure 17. TPS54332 Line Regulation

18

Submit Documentation Feedback

Copyright © 2009–2012, Texas Instruments Incorporated

Product Folder Link(s): TPS54332

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]