TPS51285A

TPS51285B

SLVSBX0 –APRIL 2013

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

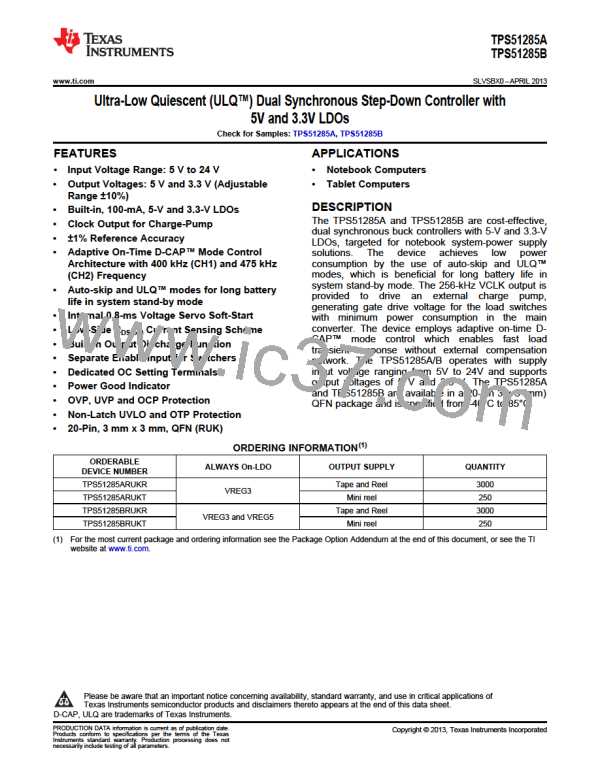

TYPICAL APPLICATION DIAGRAMS

VBAT/

VADPTOR

VIN

VBST1

DRVH1

VBST2

DRVH2

5V

output

3.3 V

output

SW1

SW2

DRVL1

VO1

DRVL2

VFB1

CS1

VFB2

CS2

VCLK

EN1

PGOOD

EN2

PGOOD

EN-5V

EN 3.3 V

3.3-V LDO

Charge pump

output

VREG5

VREG3

GND

5 V LDO

Figure 1. TYPICAL APPLICATION DIAGRAM (With Charge Pump)

2

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

Product Folder Links: TPS51285A TPS51285B

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]