TLV809J25, TLV809L30

TLV809K33, TLV809I50

SLVSA03C –JUNE 2010–REVISED FEBRUARY 2012

www.ti.com

TIMING REQUIREMENTS

At RL = 1 MΩ, CL = 50 pF, TA = +25°C.

PARAMETER

TEST CONDITIONS

VDD = VIT– + 0.2 V, VDD = VIT– – 0.2 V

MIN

TYP

MAX UNIT

tw

Pulse width at VDD

3

µs

SWITCHING CHARACTERISTICS

At RL = 1 MΩ, CL = 50 pF, TA = +25°C.

PARAMETER

TEST CONDITIONS

MIN TYP MAX UNIT

td

Delay time

VDD ≥ VIT– + 0.2 V; see timing diagram

120 200 280

ms

Propagation (delay) time,

high-to-low-level output

tPHL

VDD to RESET delay

VIL = VIT– – 0.2 V, VIH = VIT– + 0.2 V

1

µs

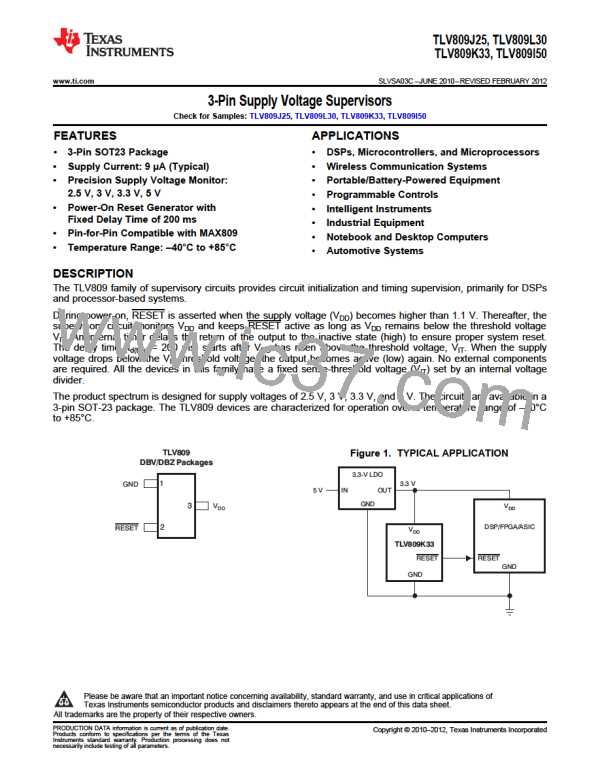

FUNCTIONAL BLOCK DIAGRAM

TLV809

Reset

Logic

+

RESET

R1

_

+

V

DD

Timer

R2

GND

Oscillator

Reference

Voltage

of 1.137 V

TIMING DIAGRAM

VDD

V(NOM)

VIT

1.1 V

t

RESET

1

0

t

td

td

For VDD < 1.1 V Undefined

Behavior of RESET Output

4

Submit Documentation Feedback

Copyright © 2010–2012, Texas Instruments Incorporated

Product Folder Link(s): TLV809J25 TLV809L30 TLV809K33 TLV809I50

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]