TAS5715

www.ti.com

SLOS645 –AUGUST 2010

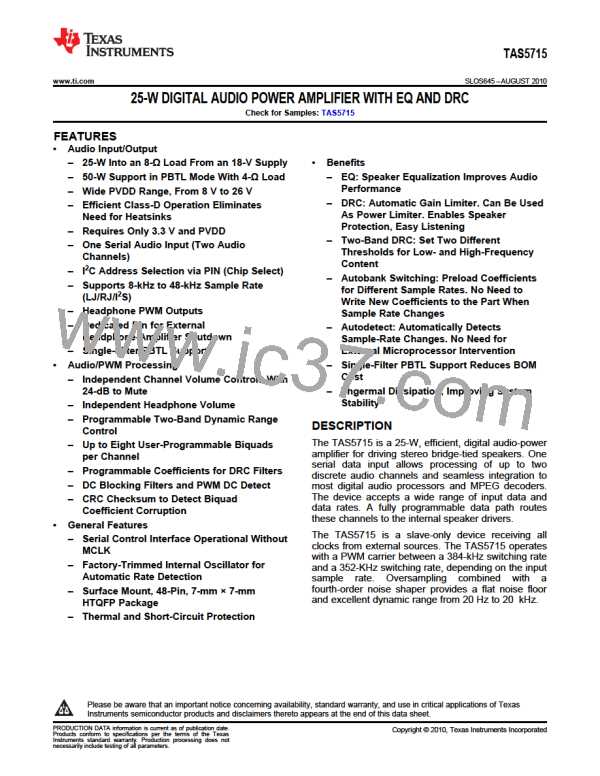

Headphone Usage

HP/SPKR

(SE/BTL)

VALID

PWM_A(L+)

PWM_C(R+)

SpkrL+/R+

SpkrL+/R+

SpkrL–/R–

50%

50%

HPL/R

t(exitSDHP)

t(enterSDHPamp)

t(mute)

t(mute)

t(exitSDHPamp)

PWM_B(L–)

PWM_D(R–)

SpkrL–/R–

t(enterSD)

t(exitSD)

FAULT = 1 Output

HPSD

(A0/FAULT)

Hi-Z (Ext. Pulldown)

I2C: SCL

SDA

Enter

ACSD

Exit

ACSD

Enable

FAULT

Disable

FAULT

Enter

ACSD

Exit

ACSD

Unmute

(if not done in

Spkr Config)

HP

Config

Spkr

Config

Mute

Unmute

Mute

PDN

T0452-01

Headphone/Speaker Configuration

PARAMETE

R

DESCRIPTION

MIN TYP MAX UNIT

t(mute)

Mute volume ramp wait time (t(volramp) given by register 0x0E <2:0>)

5 + 1.3 × t(volramp)

1 + 1.3 × t(start)

ms

ms

Exit shutdown wait time before issuing further commands to device (t(start)

given by regioster 0x1A<4:0>)

t(exitSD)

Enter shutdown wait time before issuing further commands to device (t(stop)

given by regioster 0x1A<4:0>)

t(enterSD)

1 + 1.3 × t(stop)

1 + 1.3 × t(HPchg)

1 + 1.3 × t(HPamp)

1 + 1.3 × t(HPamp)

ms

ms

ms

ms

Exit shutdown wait time before enabling external headphone amp (t(HPchg)

given by register 0x1A<6:5>)

t(exitSDHP)

Headphone amp exit shutdown wait time before unmuting (t(HPamp) given by

register 0x1C<7:4>)

t(exitSDHPamp)

t(enterSDHPamp)

Headphone amp enter shutdown wait time before entering ACSD (t(HPamp)

given by register 0x1C<7:4>)

Figure 57. Headphone Control Use Model

Speaker Configuration

•

•

•

•

•

•

•

•

•

Registers 0x07–0x0B

Register 0x19

Master/channel speaker volume

SDG = 0x30 or 0x00 (no channels in SDG)

ICD1/2 = {0xB8, 0x60}

Registers 0x11–0x12

Register 0x1A<7>

Register 0x1A<4:0>

Register 0x20<23>

Register 0x20<19>

Register 0x46<1:0>

Register 0x50<7>

Clear bit for speaker mode (HP/SPKR = 0)

Set to 0 1000 for 16.5-ms start/stop period

Set bit for Ch1 BD mode

Set bit for Ch2 BD mode

Set both bits to enable DRC1 and DRC2

Clear bit to enable EQ

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

43

Product Folder Link(s): TAS5715

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]