ꢀꢁ ꢂꢃ ꢄ ꢅ ꢆ ꢇ ꢀ ꢁꢂ ꢃ ꢄꢅ ꢈ

ꢀꢁꢂ ꢃ ꢄ ꢅ ꢉ ꢇ ꢀ ꢁꢂ ꢃ ꢄꢅ ꢄ

www.ti.com

SLES081A − JUNE 2003 – REVISED MAY 2004

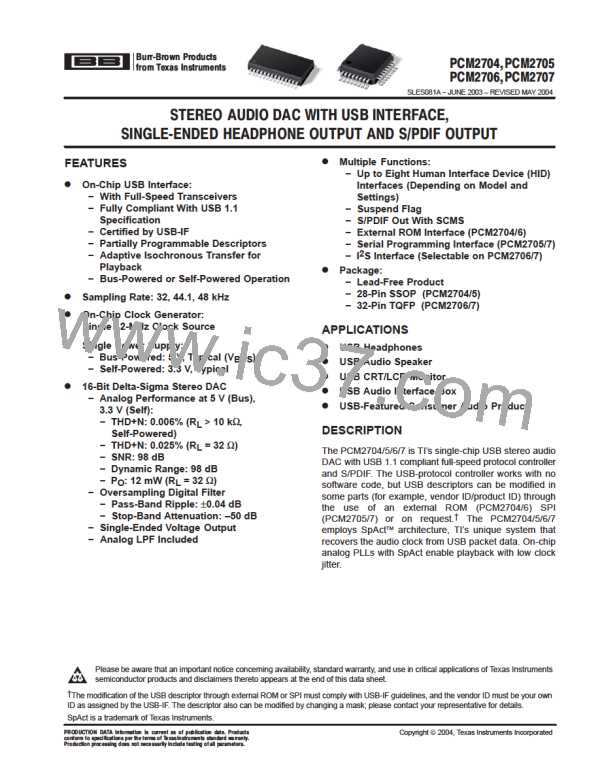

BLOCK DIAGRAM (PCM2706PJT/PCM2707PJT)

V

CCP

V

CCL

V

CCR

V

DD

PGND

AGNDL AGNDR DGND

ZGND

Power

Manager

SSPND

5-V to 3.3-V

Voltage Regulator

V

BUS

V

COM

USB

Protocol

Controller

Analog

PLL

V

OUT

L

DAC

D+

D–

Control

Endpoint

V R

OUT

S/PDIF

Encoder

DOUT

FSEL

DOUT

LRCK

BCK

FUNC0

FUNC1

FUNC2

FUNC3

2

I S I/F

EEPROM

Interface

CK

DT

SYSCK

DIN

†

ISO-Out

Endpoint

FIFO

HOST

†

HID3: Next Trackt

†

HID4: Previous Trackt

HID0/MS

HID1/MC

HID2/MD

†

HID

Endpoint

SPI

Interface

HID5: Stop

‡

†

HID6: Play/Pause

PSEL

TEST

96 MHz

Tracker

(SpAct)

PLL (×8)

XTI 12 MHz XTO

†

‡

Applies to PCM2706PJT

Applies to PCM2707PJT

9

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]