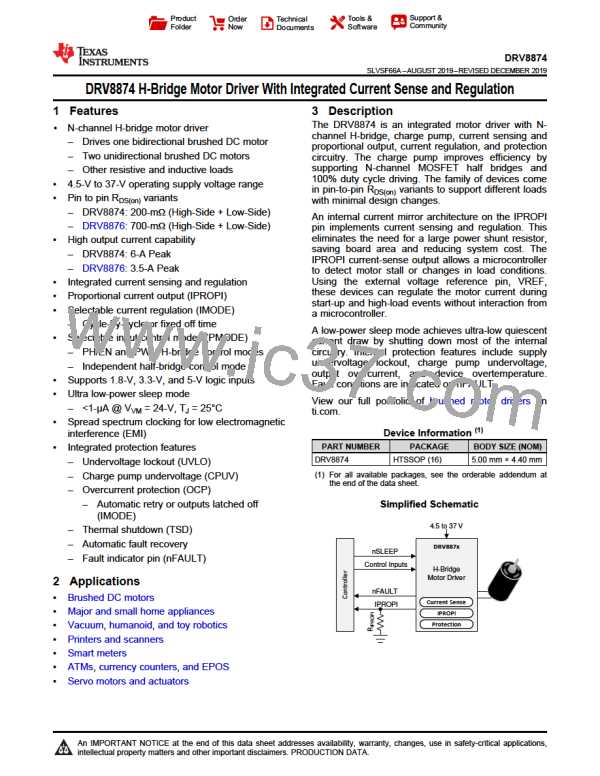

EXAMPLE BOARD LAYOUT

PWP0016J

PowerPADTM TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

(3.4)

NOTE 8

METAL COVERED

BY SOLDER MASK

(2.46)

16X (1.5)

SEE DETAILS

SYMM

16X (0.45)

1

16

(1.3) TYP

(R0.05) TYP

SYMM

(0.65)

(3.55)

(5)

NOTE 8

14X (0.65)

(

0.2) TYP

VIA

8

9

(1.35) TYP

SOLDER MASK

DEFINED PAD

(5.8)

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 10X

SOLDER MASK

OPENING

METAL UNDER

SOLDER MASK

SOLDER MASK

OPENING

METAL

EXPOSED METAL

EXPOSED METAL

0.05 MAX

ALL AROUND

0.05 MIN

ALL AROUND

NON-SOLDER MASK

DEFINED

SOLDER MASK

DEFINED

15.000

SOLDER MASK DETAILS

4223595/A 03/2017

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

7. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature

numbers SLMA002 (www.ti.com/lit/slma002) and SLMA004 (www.ti.com/lit/slma004).

8. Size of metal pad may vary due to creepage requirement.

9. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged

or tented.

www.ti.com

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]