CD4541B

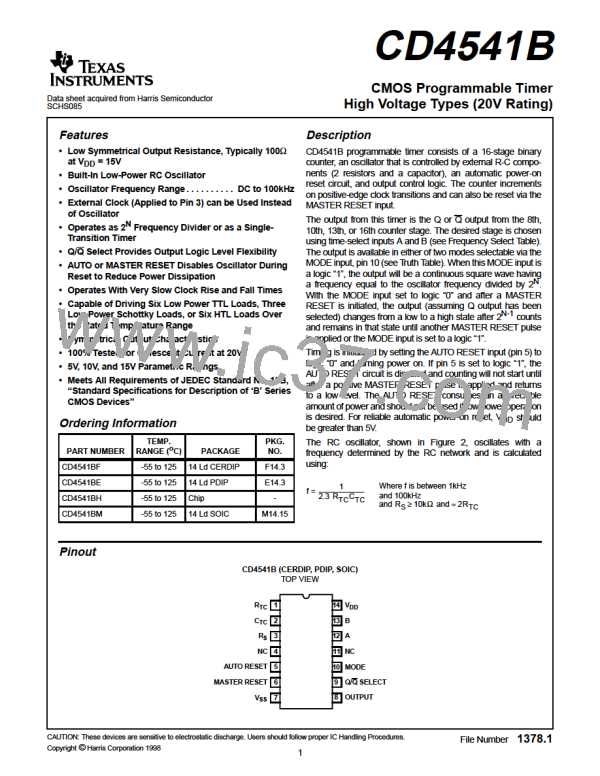

Functional Diagram

12

13

1

A

B

R

C

TC

TC

2

3

8

R

Q

S

5

AR

MR

6

10

V

V

= PIN 14

= PIN 7

DD

SS

MODE

9

Q/Q

SELECT

Functional Block Diagram

12 13

†A †B

R

N

P

8

Q

1 OF 3

MUX

9

N

P

16

†Q/Q SELECT

2

OR

3

10

13

8

2

2

2

†R

S

V

2

DD

8-STAGE

COUNTER

8-STAGE

COUNTER

OSC

†C

TC

†R

TC

1

R

R

10

†MODE

R

5

PWR ON

RESET

V

SS

V

V

= 14

= 7

DD

SS

† All inputs are protected by CMOS Protection Network.

NC = 4, 11

6

MANUAL RESET†

FIGURE 1.

FREQUENCY SELECTION TABLE

NO. OF

N

A

0

0

1

1

B

0

1

0

1

STAGES N

COUNT 2

8192

3

13

10

8

TO CLOCK

CKT

1024

R

S

256

INTERNAL

RESET

16

65536

C

2

1

TC

TRUTH TABLE

STATE

R

TC

PIN

5

0

Auto Reset On

Master Reset Off

1

Auto Reset Disable

Master Reset On

6

FIGURE 2. RC OSCILLATOR CIRCUIT

9

Output Initially Low After

Reset (Q)

Output Initially High After

Reset (Q)

10

Single Transition Mode

Recycle Mode

2

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]