bq20z80-V101

www.ti.com

SLUS625D–SEPTEMBER 2004–REVISED OCTOBER 2005

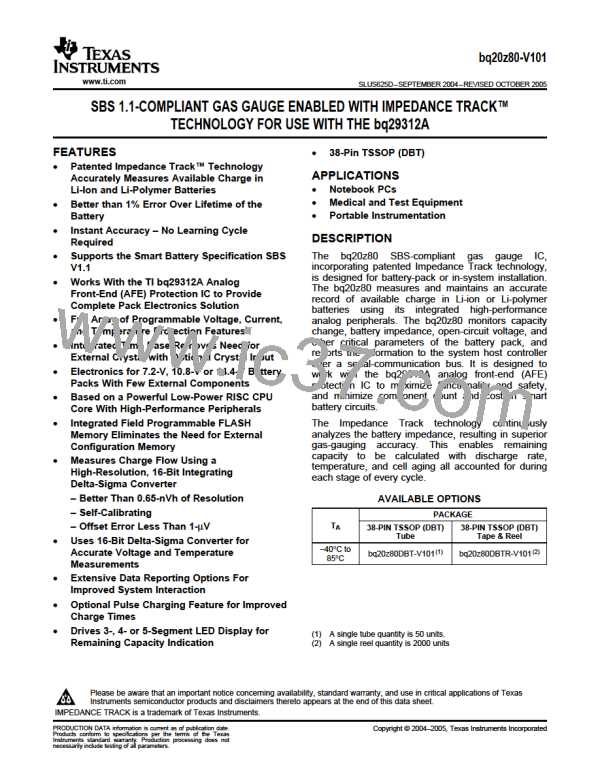

SMBus TIMING SPECIFICATIONS

VDD = 3 V to 3.6 V, TA = –40°C to 85°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX UNIT

fSMB

SMBus operating frequency

SMBus master clock frequency

Bus free time between start and stop

Hold time after (repeated) start

Repeated start setup time

Stop setup time

Slave mode, SMBC 50% duty cycle

10

100

kHz

fMAS

Master mode, no clock low slave extend

51.2

tBUF

4.7

4

tHD:STA

tSU:STA

tSU:STO

µs

4.7

4

Receive mode

Transmit mode

0

tHD:DAT

Data hold time

300

250

(1)25

4.7

(2)4

ns

tSU:DAT

tTIMEOUT

tLOW

Data setup time

Error signal/detect

35

ms

Clock low period

µs

tHIGH

Clock high period

50

(3)25

(4)10

300

tLOW:SEXT

tLOW:MEXT

tF

Cumulative clock low slave extend time

Cumulative clock low master extend time

Clock/data fall time

ms

ns

(VILMAX– 0.15 V) to (VIHMIN + 0.15 V)

0.9 VDD to (VILMAX – 0.15 V)

tR

Clock/data rise time

1000

(1) The bq20z80 times out when any clock low exceeds tTIMEOUT

.

(2) tHIGH:MAX. is minimum bus idle time. SMBC = 1 for t > 50 µs causes reset of any transaction involving the bq20z80 that is in progress.

(3) tLOW:SEXT is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

(4) tLOW:MEXT is the cumulative time a master device is allowed to extend the clock cycles in one message from initial start to the stop.

SMBus TIMING DIAGRAM

6

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]