bq20z80-V101

www.ti.com

SLUS625D–SEPTEMBER 2004–REVISED OCTOBER 2005

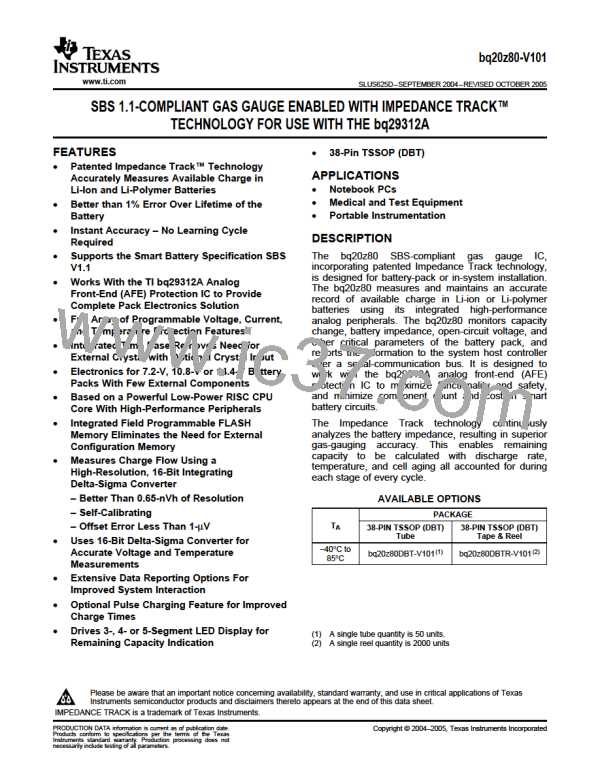

PLL SWITCHING CHARACTERISTICS

VDD = 3 V to 3.6 V, TA = –40°C to 85°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

0.5% frequency error

MIN

TYP

MAX

UNIT

(1)

t(SP)

Start-up time

2

5

ms

(1) The frequency error is measured from the trimmed frequency of the internal system clock which is 128 oscillator frequency, nominally

4.194 MHz.

OSCILLATOR

VDD = 3 V to 3.6 V, TA = –40°C to 85°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

ROSC = 100 kΩ

MIN

–2%

TYP

0.25%

0.25%

MAX UNIT

2%

1%

f(exo)

Frequency error from 32.768 kHz

ROSC = 100 kΩ, VDD = 3.3 V

XCK1 = 12-pF XTAL

ROSC = 100 kΩ

–1%

–0.25%

0.25%

(1)

f(sxo)

Start-up time

250

200

µs

XCK1 = 12-pF XTAL

ms

(1) The start-up time is defined as the time it takes for the oscillator output frequency to be within 1% of the specified frequency.

DATA FLASH MEMORY CHARACTERISTICS

VDD = 3 V to 3.6 V, TA = –40°C to 85°C (unless otherwise noted)

PARAMETER

Data retention

TEST CONDITIONS

MIN

(1)10

TYP

MAX

UNIT

Years

Cycles

ms

tDR

(1)

(1)

(1)

Flash programming write-cycles

Word programming time

20,000

t(WORDPROG)

I(DDPROG)

2

Flash-write supply current

8

15

mA

(1) Assured by design. Not production tested

REGISTER BACKUP

VDD = 3 V to 3.6 V, TA = –40°C to 85°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

V(RBI) > 3 V, VDD < VIT

MIN

TYP

10

MAX UNIT

I(RBI)

RBI data-retention input current

RBI data-retention voltage(1)

100

nA

V

V(RBI)

1.3

(1) Specified by design. Not production tested.

5

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]