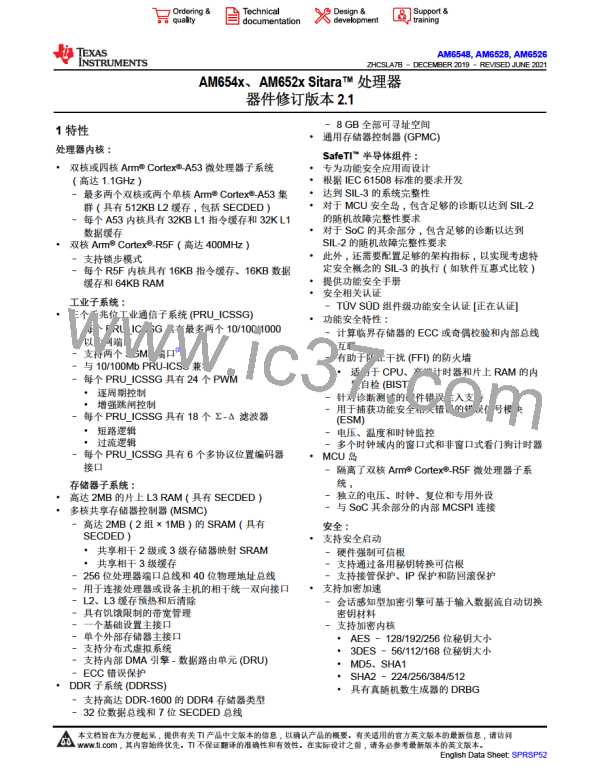

AM6548, AM6528, AM6526

ZHCSLA7B –DECEMBER 2019 –REVISED JUNE 2021

www.ti.com.cn

表6-27. GPMC0 Signal Descriptions (continued)

PIN TYPE

SIGNAL NAME [1]

DESCRIPTION [2]

BALL [4]

[3]

GPMC Data 6 Input/Output in A/D non-multiplexed mode

and additionally Address 7 Output in A/D multiplexed

mode

GPMC0_AD6

GPMC0_AD7

GPMC0_AD8

GPMC0_AD9

GPMC0_AD10

GPMC0_AD11

GPMC0_AD12

GPMC0_AD13

GPMC0_AD14

IO

IO

IO

IO

IO

IO

IO

IO

IO

N28

GPMC Data 7 Input/Output in A/D non-multiplexed mode

and additionally Address 8 Output in A/D multiplexed

mode

M25

N23

M26

P28

P27

N26

N25

P24

GPMC Data 8 Input/Output in A/D non-multiplexed mode

and additionally Address 9 Output in A/D multiplexed

mode

GPMC Data 9 Input/Output in A/D non-multiplexed mode

and additionally Address 10 Output in A/D multiplexed

mode

GPMC Data 10 Input/Output in A/D non-multiplexed

mode and additionally Address 11 Output in A/D

multiplexed mode

GPMC Data 11 Input/Output in A/D non-multiplexed

mode and additionally Address 12 Output in A/D

multiplexed mode

GPMC Data 12 Input/Output in A/D non-multiplexed

mode and additionally Address 13 Output in A/D

multiplexed mode

GPMC Data 13 Input/Output in A/D non-multiplexed

mode and additionally Address 14 Output in A/D

multiplexed mode

GPMC Data 14 Input/Output in A/D non-multiplexed

mode and additionally Address 15 Output in A/D

multiplexed mode

GPMC Data 15 Input/Output in A/D non-multiplexed

mode and additionally Address 16 Output in A/D

multiplexed mode

GPMC0_AD15

IO

O

R27

T28

GPMC Lower-Byte Enable (active low) or Command

Latch Enable

GPMC0_BE0n_CLE

GPMC0_BE1n

GPMC0_CSn0

GPMC0_CSn1

GPMC0_CSn2

GPMC0_CSn3

GPMC0_WAIT0

GPMC0_WAIT1

GPMC Upper-Byte Enable (active low)

GPMC Chip Select 0 (active low)

GPMC Chip Select 1 (active low)

GPMC Chip Select 2 (active low)

GPMC Chip Select 3 (active low)

GPMC External Indication of Wait

GPMC External Indication of Wait

O

O

O

O

O

I

P23

R24

T23

R25

T27

R26

R23

I

6.3.12 HyperBus

Note

HyperBus is not available on this device.

6.3.12.1 MCU Domain

表6-28. HYPERBUS0 Signal Descriptions

PIN TYPE

SIGNAL NAME [1]

DESCRIPTION [2]

BALL [4]

[3]

MCU_HYPERBUS0_CK

MCU_HYPERBUS0_CKn

MCU_HYPERBUS0_INTn

Hyperbus Differential Clock (positive)

Hyperbus Differential Clock (negative)

Hyperbus Interrupt (active low)

O

O

I

V1

U1

P2

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

79

Product Folder Links: AM6548 AM6528 AM6526

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]