ADS1274

ADS1278

SBAS367F –JUNE 2007–REVISED FEBRUARY 2011

www.ti.com

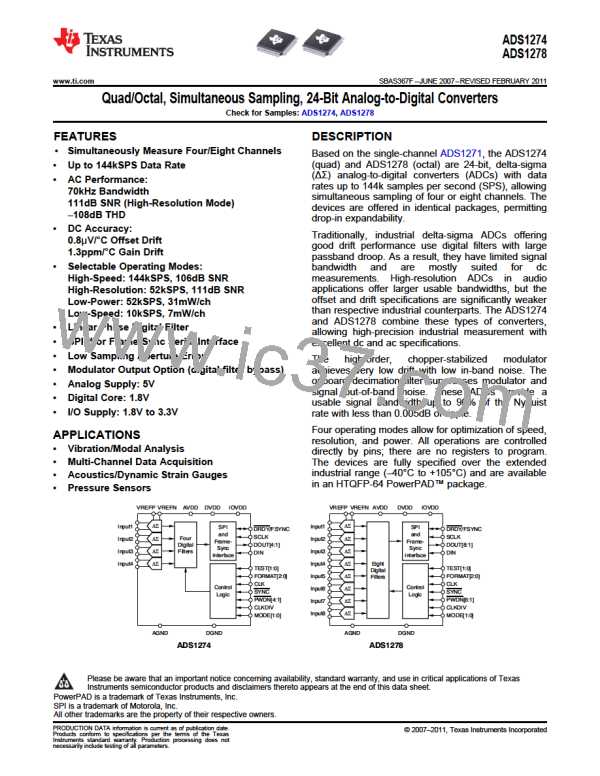

SPI FORMAT TIMING

tCLK

tCPW

CLK

· · ·

tCPW

tCD

tCONV

DRDY

tSD

tDS

tSCLK

tSPW

SCLK

tSPW

tDOPD

tMSBPD

Bit 23 (MSB)

tDOHD

Bit 22

tDIST

Bit 21

DOUT

DIN

tDIHD

SPI FORMAT TIMING SPECIFICATION

For TA = –40°C to +105°C, IOVDD = 1.65V to 3.6V, and DVDD = 1.65V to 1.95V, unless otherwise noted.

SYMBOL

tCLK

PARAMETER

MIN

37

TYP

MAX

UNIT

ns

(1)

CLK period (1/fCLK

)

10,000

tCPW

CLK positive or negative pulse width

15

ns

(2)

tCONV

Conversion period (1/fDATA

)

256

2560

16

tCLK

ns

(3)

tCD

Falling edge of CLK to falling edge of DRDY

Falling edge of DRDY to rising edge of first SCLK to retrieve data

DRDY falling edge to DOUT MSB valid (propagation delay)

Falling edge of SCLK to rising edge of DRDY

SCLK period

22

18

(3)

tDS

1

tCLK

ns

tMSBPD

(3)

tSD

ns

(4)

tSCLK

1

0.4

10

tCLK

tCLK

ns

tSPW

SCLK positive or negative pulse width

(3)(5)

tDOHD

SCLK falling edge to new DOUT invalid (hold time)

32

26

ns

ns(6)

(3)

tDOPD

SCLK falling edge to new DOUT valid (propagation delay)

tDIST

New DIN valid to falling edge of SCLK (setup time)

Old DIN valid to falling edge of SCLK (hold time)

6

6

ns

(5)

tDIHD

ns

(1) fCLK = 27MHz maximum.

(2) Depends on MODE[1:0] and CLKDIV selection. See Table 8 (fCLK/fDATA).

(3) Load on DRDY and DOUT = 20pF.

(4) For best performance, limit fSCLK/fCLK to ratios of 1, 1/2, 1/4, 1/8, etc.

(5) tDOHD (DOUT hold time) and tDIHD (DIN hold time) are specified under opposite worst-case conditions (digital supply voltage and

ambient temperature). Under equal conditions, with DOUT connected directly to DIN, the timing margin is > 4ns.

(6) DOUT1, TDM mode, IOVDD = 3.15V to 3.45V, and DVDD = 1.7V to 1.9V.

8

Submit Documentation Feedback

© 2007–2011, Texas Instruments Incorporated

Product Folder Link(s): ADS1274 ADS1278

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]