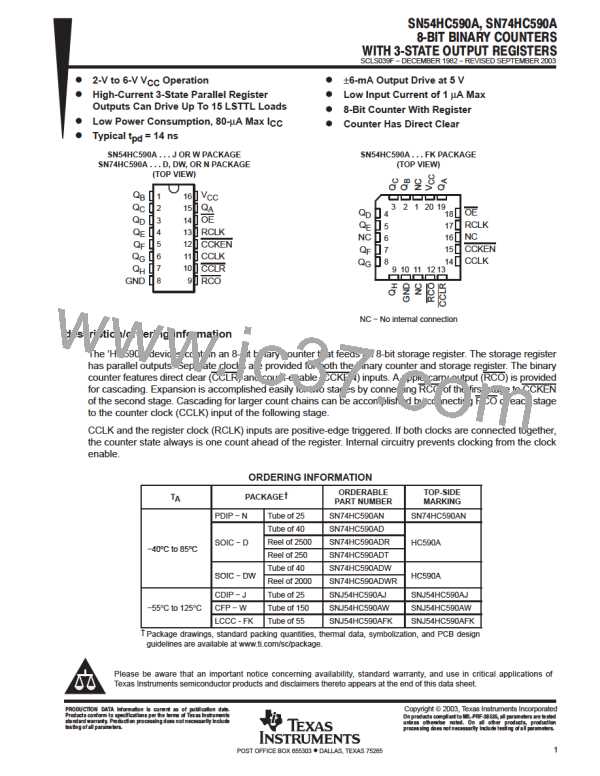

ꢀ ꢁꢂ ꢃꢄ ꢅ ꢂꢆ ꢇꢈ ꢉ ꢀ ꢁꢊ ꢃ ꢄꢅꢂ ꢆ ꢇ ꢈ

ꢋꢌ ꢍꢎ ꢏ ꢍ ꢎ ꢁꢈ ꢐꢑ ꢅꢒ ꢓꢁ ꢏꢔ ꢐꢀ

ꢕꢎ ꢏ ꢄ ꢖ ꢌꢀꢏꢈꢏ ꢔ ꢒꢓꢏ ꢗꢓ ꢏ ꢐꢔ ꢘ ꢎꢀ ꢏꢔ ꢐꢀ

SCLS039F − DECEMBER 1982 − REVISED SEPTEMBER 2003

timing diagram

OE

CCLR

CCKEN

CCLK

RCLK

COUNTER

(internal)

Don’t

Care

Hex 01

Hex 02

Hex 03

Hex 04

Hex 05

Hex FD

Hex FE

Hex 05

Hex FF

Hex 00

Hex01

Hex 00

Hex 00

Hi-Z

Don’t

Care

Q −Q

Hex 00

Hex 01

Hex 01

A

H

RCO

TIMING SEQUENCE

1. Clear Counter (asynchronous).

2. Count up: 0x01. Store 0x00 in register.

3. Inhibit counter clock (CCKEN = HIGH). Store 0x01 in register.

4. Count 0x02, 0x03.

5. 3-state the outputs

6. Count up: 0x04

7. Enable outputs.

8. Continue up: 0x05

9. Store 0x05 in register.

10.Continue counting: 0x06...0xFD, 0xFE, 0xFF, 0x00, etc.

11. Store 0x00 in register.

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]