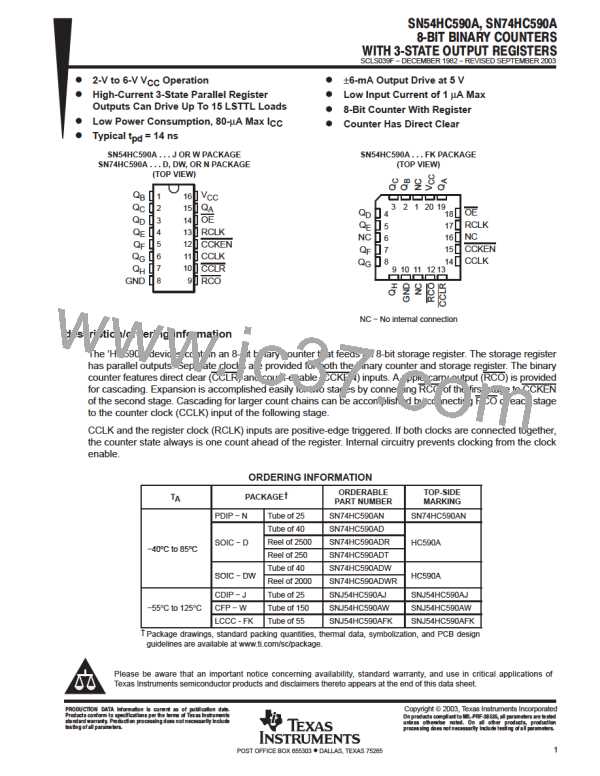

ꢀ ꢁꢂ ꢃꢄ ꢅ ꢂꢆ ꢇꢈ ꢉ ꢀ ꢁꢊ ꢃ ꢄꢅꢂ ꢆ ꢇ ꢈ

ꢋꢌ ꢍꢎ ꢏ ꢍ ꢎ ꢁꢈ ꢐꢑ ꢅꢒ ꢓꢁ ꢏꢔ ꢐꢀ

ꢕꢎ ꢏ ꢄ ꢖ ꢌꢀꢏꢈꢏ ꢔ ꢒꢓꢏ ꢗꢓ ꢏ ꢐꢔ ꢘ ꢎꢀ ꢏꢔ ꢐꢀ

SCLS039F − DECEMBER 1982 − REVISED SEPTEMBER 2003

timing requirements over recommended operating free-air temperature range (unless otherwise

noted)

T

= 25°C

SN54HC590A SN74HC590A

A

V

UNIT

CC

MIN

MAX

4

MIN

MAX

2.5

13

MIN

MAX

3.2

16

2 V

4.5 V

6 V

20

f

Clock frequency

Pulse duration

MHz

clock

24

16

19

2 V

125

25

200

38

155

31

4.5 V

6 V

CCLK or RCLK high or low

CCLR low

21

32

26

t

w

ns

2 V

100

20

150

30

125

25

4.5 V

6 V

17

26

21

2 V

100

20

150

30

125

25

4.5 V

6 V

CCKEN low before CCLK↑

CCLR high (inactive) before CCLK↑

17

26

21

2 V

100

20

150

30

125

25

4.5 V

6 V

t

t

Setup time

ns

ns

su

17

26

21

2 V

100

20

150

30

125

25

†

4.5 V

6 V

CCLK↑ before RCLK↑

17

26

21

2 V

50

75

60

Hold time

CCKEN low after CCLK↑

4.5 V

6 V

10

15

12

h

9

13

11

†

This setup time ensures that the register gets stable data from the counter outputs. The clocks may be tied together, in which case the register

is one clock pulse behind the counter.

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]