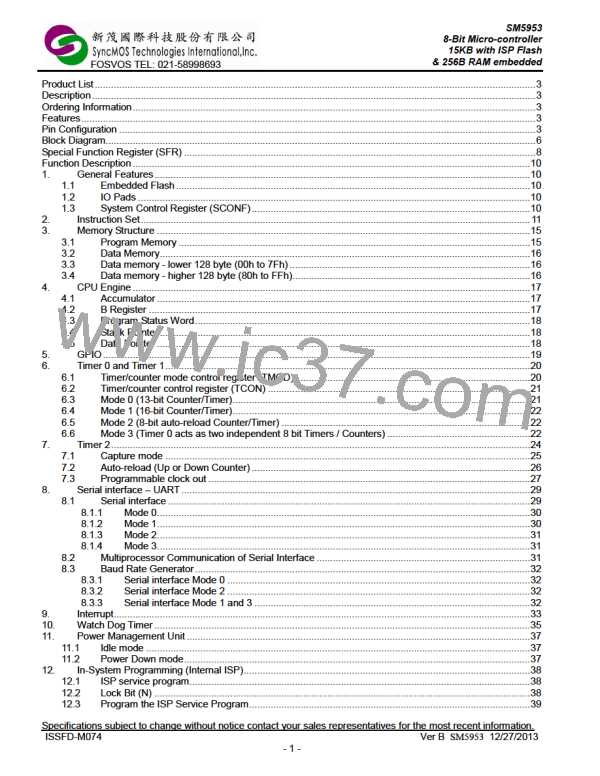

SM5953

8-Bit Micro-controller

15KB with ISP Flash

& 256B RAM embedded

4. CPU Engine

The SM5953 engine is composed of four components:

(1)

(2)

(3)

(4)

Control unit

Arithmetic – logic unit

Memory control unit

RAM and SFR control unit

The SM5953 engine allows to fetch instruction from program memory and to execute using RAM or SFR. The

following chapter describes the main engine register.

Mnemonic

Description

Accumulator

Dir.

Bit 7

Bit 6

8051 Core

E0h ACC.7 ACC.6 ACC.5 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

RST

ACC

B

00H

00H

B register

F0h

B.7

B.6

B.5

B.4

B.3

B.2

B.1

B.0

Program status

word

PSW

D0h

CY

AC

F0

RS[1:0]

OV

PSW.1

P

00H

SP

DPL

DPH

Stack Pointer

Data pointer low

Data pointer high

81h

82h

83h

SP[7:0]

DPL[7:0]

DPH[7:0]

07H

00H

00H

4.1 Accumulator

ACC is the Accumulator register. Most instructions use the accumulator to store the operand.

Mnemonic: ACC

Address: E0h

Reset

00h

7

6

5

4

3

2

1

0

ACC.7 ACC.6 ACC05 ACC.4 ACC.3 ACC.2 ACC.1 ACC.0

ACC[7:0]: The A (or ACC) register is the standard 8052 accumulator.

4.2 B Register

The B register is used during multiply and divide instructions. It can also be used as a scratch pad register to store

temporary data.

Mnemonic: B

Address: F0h

7

B.7

6

B.6

5

B.5

4

B.4

3

B.3

2

B.2

1

B.1

0

B.0

Reset

00h

B[7:0]: The B register is the standard 8052 register that serves as a second accumulator.

Specifications subject to change without notice contact your sales representatives for the most recent information.

ISSFD-M074

Ver B SM5953 12/27/2013

- 17 -

SYNCMOS [ SYNCMOS TECHNOLOGIES,INC ]

SYNCMOS [ SYNCMOS TECHNOLOGIES,INC ]