SMS44

S

T

A

R

T

Typical Write Operation

(Standard memory device type)

S

T

O

P

Device Type Bus

Master

SDA

Address Address

R

/

W

B B

A

D D D D D D D D

A

7

A A A A A A A

6 5 3 2 1 0

A A

1 0 1 0

7

6 5 4 3 2 1 0

4

8

2

1

A

C

K

A

C

K

A

C

K

Slave

Up to 15

additional bytes

can be written

before issuing

the stop.

S

S

T

O

P

T

A

R

T

Typical Reading Operation

(Alternate memory device type)

A

C

K

A

C

K

Master

SDA

R

/

W

B B

A A

A A A A A A A A

3 2 1 0

D D D D D D D D

A

8

1 0 1 1

7

6 5 4

7

6 5 4 3 2 1 0

2

1

A

C

K

Slave

The host may continue

clocking out data so long as

it provides an ACK response

after each byte.

S

T

A

R

T

S

T

O

P

Writing Configuration Registers

Master

SDA

R

/

B B

A A

D D D D D D D D

C C C C C C C C

X

0 1

1 0

7

6 5 4 3 2 1 0

7

6

5

4

3

2

1

0

W

2

1

A

C

K

A

C

K

A

C

K

Slave

S

T

A

R

T

S

T

A

R

T

S

A

A

C

K

T

Reading the Configuration Register

C

Master

SDA

O

K

P

B B

A A

B B

A A

R

/

W

R

D D D D D D D D

C C C C C C C C

X

/

X

0 1

1 0

0 1

1 0

7

6 5 4 3 2 1 0

7

6 5 4 3 2 1 0

2

1

2

1

W

A

C

K

A

C

K

Slave

2047 Fig10 2.1

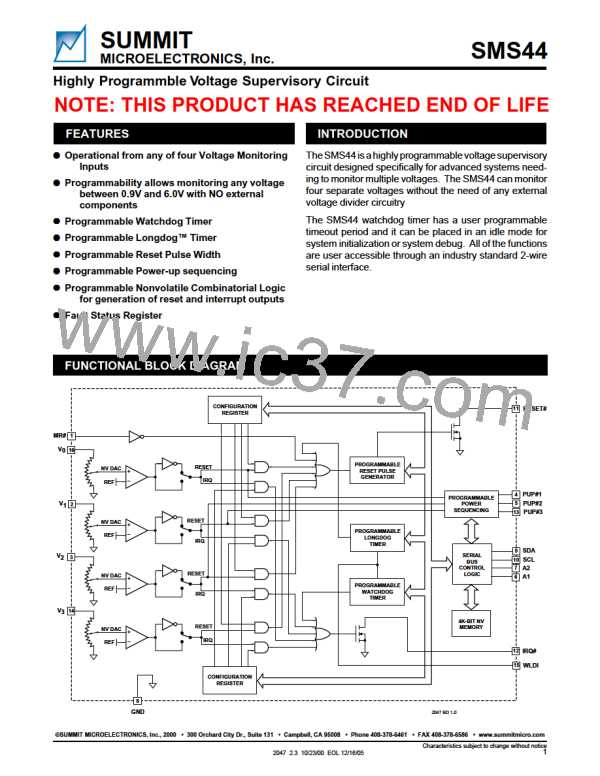

Fi gure 10 .

Read and Wri te Operati ons

The high order bits of the address byte remain constant. ten. As with the byte-write operation, all inputs are

Should the master transmit more than 16 bytes, prior to disabledduringtheinternalwritecycle. RefertoFigure10

generating the STOP condition, the address counter will for the address, ACKnowledge, and data transfer se-

“roll over” and the previously written data will be overwrit- quence.

SUMMIT MICROELECTRONICS, Inc.

2047 2.3 10/23/00

13

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]