SMM153

I2C PROGRAMMING INFORMATION (CONTINUED)

S

T

A

R

T

S

T

A

R

T

Configuration

Register Address

Master

Slave

Bus Address

Bus Address

S

A

1

S

A

0

S

A

3

S

A

2

S

A

1

S

A

0

A

2

A

1

A

0

C

7

C

6

C

5

C

4

C

3

C

2

C

1

C

0

A

2

A

1

A

0

W

R

1

0

A

C

K

A

C

K

A

C

K

N

A

C

K

S

T

O

P

A

C

K

A

C

K

Master

Slave

Data (1)

Data (n)

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

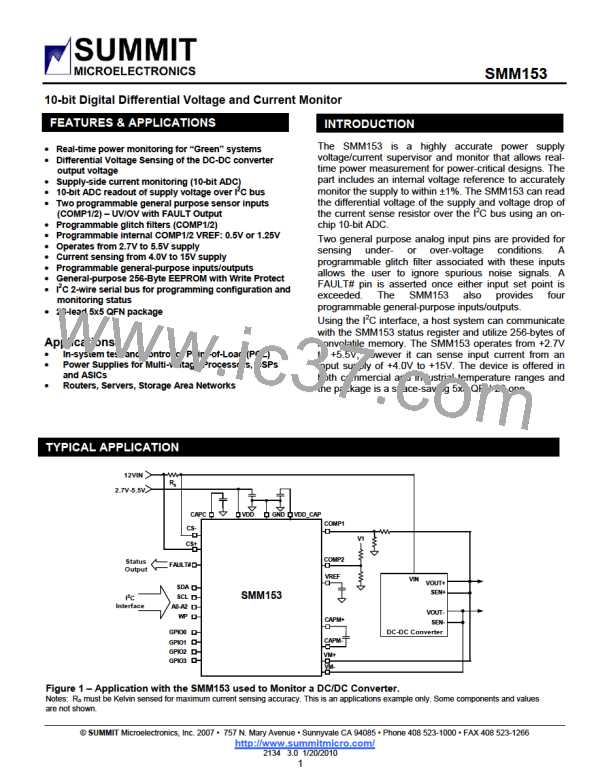

Figure 9 - Configuration Register Read

S

T

A

R

T

S

T

O

P

Configuration

Register Address

Master

Slave

Bus Address

Data

S

A

1

S

A

0

A

2

A

1

A

0

C

7

C

6

C

5

C

4

C

3

C

2

C

1

C

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

W

1

0

A

C

K

A

C

K

A

C

K

Figure 10 – General Purpose Memory Byte Write

S

T

A

R

T

Configuration

Register Address

Master

Bus Address

Data (1)

S

A

1

S

A

0

A

2

A

1

A

0

C

7

C

6

C

5

C

4

C

3

C

2

C

1

C

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

W

1

0

Slave

A

C

K

A

C

K

A

C

K

S

T

O

P

Master

Slave

Data (2)

Data (16)

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

D

7

D

6

D

5

D

2

D

1

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

A

C

K

A

C

K

A

C

K

Figure 11 - General Purpose Memory Page Write

Summit Microelectronics, Inc

2134 3.0 1/20/2010

15

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]