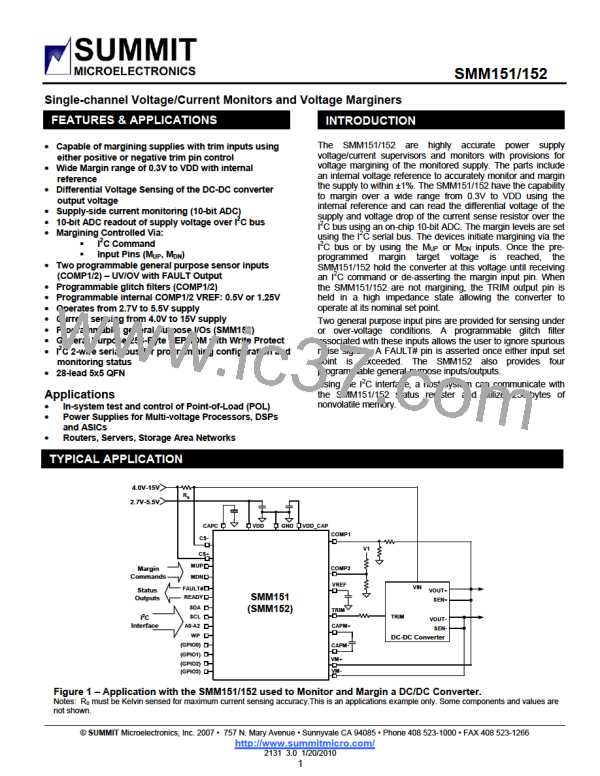

SMM151/152

INTERNAL BLOCK DIAGRAM

VREF

READY

FAULT#

VDD

VDD_CAP

GND

COMP1

COMP2

OV/UV

OV/UV

VREF

0.5V/1.25V

Glitch

Filter

Output

Control

VREF = 1.25V

50kΩ

Up/Dn

MUP

TRIM

Digital

Comparator

Margin

Target

Control

Logic

8-bit DAC

MDN

Halt

SW1

50kΩ

Clock

MUX

A0

A1

SW2

10Bit

ADC

I2C

Interface

A2

SCL

SDA

CAPM+

CAPM-

WP

25kΩ

25kΩ

VM+

VM-

GPIO0

GPIO1

GPIO2

GPIO3

EE

Control

Logic

Configuration

Registers

& Memory

CAPC

CS+

SMM152

250kΩ

DIFF

AMP

CS-

Figure 2 – SMM151 and SMM152 Controller Internal Block Diagram.

PACKAGE AND PIN DESCRIPTION

Summit Microelectronics, Inc

2131 3.0 1/20/2010

3

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]