Electrical characteristics

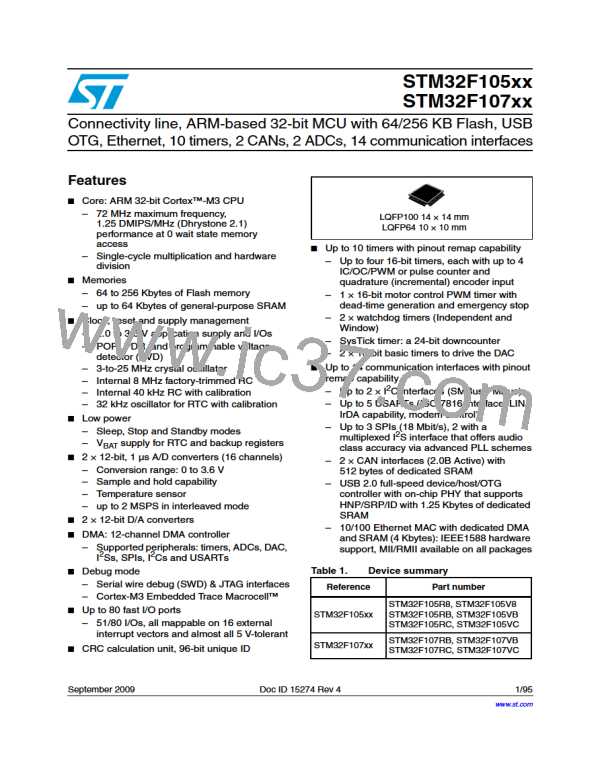

STM32F105xx, STM32F107xx

Output driving current

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink

+20 mA (with a relaxed V ).

OL

In the user application, the number of I/O pins which can drive current must be limited to

respect the absolute maximum rating specified in Section 5.2:

G

G

The sum of the currents sourced by all the I/Os on V

consumption of the MCU sourced on V

plus the maximum Run

cannot exceed the absolute maximum rating

DD,

DD,

I

(see Table 7).

VDD

The sum of the currents sunk by all the I/Os on V plus the maximum Run

SS

consumption of the MCU sunk on V cannot exceed the absolute maximum rating

SS

I

(see Table 7).

VSS

Output voltage levels

Unless otherwise specified, the parameters given in Table 36 are derived from tests

performed under ambient temperature and V supply voltage conditions summarized in

DD

Table 9. All I/Os are CMOS and TTL compliant.

Table 36. Output voltage characteristics

Symbol

Parameter

Conditions

Min

Max

Unit

Output low level voltage for an I/O pin

when 8 pins are sunk at same time

(1)

VOL

0.4

TTL port

IIO = +8 mA

V

Output high level voltage for an I/O pin

when 8 pins are sourced at same time

(2)

2.7 V < VDD < 3.6 V

VOH

VDD–0.4

Output low level voltage for an I/O pin

when 8 pins are sunk at same time

(1)

VOL

0.4

1.3

0.4

CMOS port

IIO =+ 8mA

V

V

V

Output high level voltage for an I/O pin

when 8 pins are sourced at same time

(2)

2.7 V < VDD < 3.6 V

VOH

2.4

Output low level voltage for an I/O pin

when 8 pins are sunk at same time

(1)(3)

VOL

IIO = +20 mA

2.7 V < VDD < 3.6 V

Output high level voltage for an I/O pin

when 8 pins are sourced at same time

(2)(3)

VOH

VDD–1.3

Output low level voltage for an I/O pin

when 8 pins are sunk at same time

(1)(3)

VOL

IIO = +6 mA

2 V < VDD < 2.7 V

Output high level voltage for an I/O pin

when 8 pins are sourced at same time

(2)(3)

VOH

VDD–0.4

1. The IIO current sunk by the device must always respect the absolute maximum rating specified in Table 7

and the sum of IIO (I/O ports and control pins) must not exceed IVSS

.

2. The IIO current sourced by the device must always respect the absolute maximum rating specified in

Table 7 and the sum of IIO (I/O ports and control pins) must not exceed IVDD

.

3. Based on characterization data, not tested in production.

54/95

Doc ID 15274 Rev 4

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]