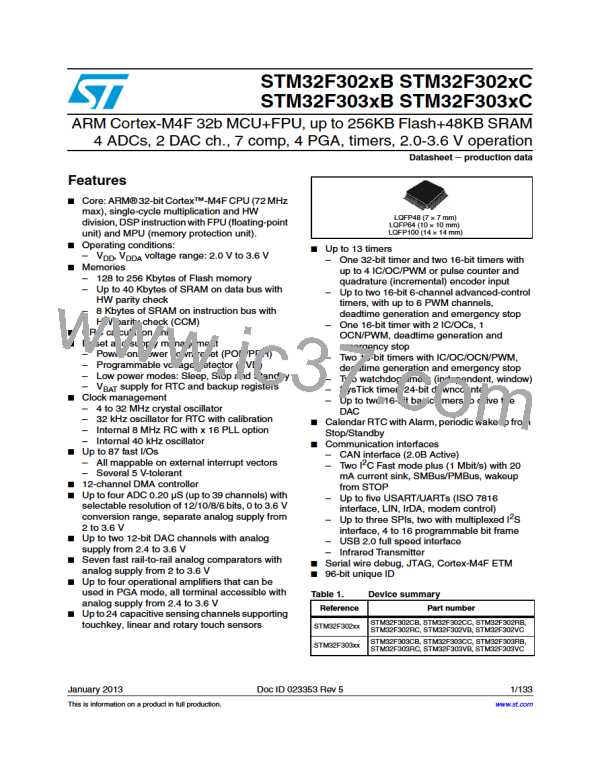

Memory mapping

STM32F302xx/STM32F303xx

Table 18. STM32F30xB/C memory map and peripheral register boundary addresses

(continued)

Size

(bytes)

Bus

Boundary address

Peripheral

0x4000 8000 - 0x4000 FFFF

0x4000 7800 - 0x4000 7FFF

0x4000 7400 - 0x4000 77FF

0x4000 7000 - 0x4000 73FF

0x4000 6C00 - 0x4000 6FFF

0x4000 6800 - 0x4000 6BFF

0x4000 6400 - 0x4000 67FF

0x4000 6000 - 0x4000 63FF

0x4000 5C00 - 0x4000 5FFF

0x4000 5800 - 0x4000 5BFF

0x4000 5400 - 0x4000 57FF

0x4000 5000 - 0x4000 53FF

0x4000 4C00 - 0x4000 4FFF

0x4000 4800 - 0x4000 4BFF

0x4000 4400 - 0x4000 47FF

0x4000 4000 - 0x4000 43FF

0x4000 3C00 - 0x4000 3FFF

0x4000 3800 - 0x4000 3BFF

0x4000 3400 - 0x4000 37FF

0x4000 3000 - 0x4000 33FF

0x4000 2C00 - 0x4000 2FFF

0x4000 2800 - 0x4000 2BFF

0x4000 1800 - 0x4000 27FF

0x4000 1400 - 0x4000 17FF

0x4000 1000 - 0x4000 13FF

0x4000 0C00 - 0x4000 0FFF

0x4000 0800 - 0x4000 0BFF

0x4000 0400 - 0x4000 07FF

0x4000 0000 - 0x4000 03FF

32 K

2 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

1 K

4 K

1 K

1 K

1 K

1 K

1 K

1 K

Reserved

Reserved

DAC (dual)

PWR

Reserved

Reserved

bxCAN

USB SRAM 512 bytes

USB device FS

I2C2

I2C1

UART5

UART4

USART3

USART2

I2S3ext

SPI3/I2S3

SPI2/I2S2

I2S2ext

IWDG

APB1

WWDG

RTC

Reserved

TIM7

TIM6

Reserved

TIM4

TIM3

TIM2

52/133

Doc ID 023353 Rev 5

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]