Three Port 10/100 Managed Ethernet Switch with MII

Datasheet

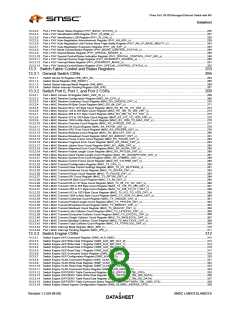

13.3.3.17 Switch Engine Port Ingress Configuration Register (SWE_PORT_INGRSS_CFG)..................................................................................... 331

13.3.3.18 Switch Engine Admit Only VLAN Register (SWE_ADMT_ONLY_VLAN)..................................................................................................... 332

13.3.3.19 Switch Engine Port State Register (SWE_PORT_STATE)........................................................................................................................... 333

13.3.3.20 Switch Engine Priority to Queue Register (SWE_PRI_TO_QUE) ................................................................................................................ 334

13.3.3.21 Switch Engine Port Mirroring Register (SWE_PORT_MIRROR).................................................................................................................. 335

13.3.3.22 Switch Engine Ingress Port Type Register (SWE_INGRSS_PORT_TYP)................................................................................................... 336

13.3.3.23 Switch Engine Broadcast Throttling Register (SWE_BCST_THROT).......................................................................................................... 337

13.3.3.24 Switch Engine Admit Non Member Register (SWE_ADMT_N_MEMBER)................................................................................................... 338

13.3.3.25 Switch Engine Ingress Rate Configuration Register (SWE_INGRSS_RATE_CFG) .................................................................................... 339

13.3.3.26 Switch Engine Ingress Rate Command Register (SWE_INGRSS_RATE_CMD)......................................................................................... 340

13.3.3.26.1Ingress Rate Table Registers.................................................................................................341

13.3.3.27 Switch Engine Ingress Rate Command Status Register (SWE_INGRSS_RATE_CMD_STS) .................................................................... 342

13.3.3.28 Switch Engine Ingress Rate Write Data Register (SWE_INGRSS_RATE_WR_DATA)............................................................................... 343

13.3.3.29 Switch Engine Ingress Rate Read Data Register (SWE_INGRSS_RATE_RD_DATA) ............................................................................... 344

13.3.3.30 Switch Engine Port 0 Ingress Filtered Count Register (SWE_FILTERED_CNT_MII) .................................................................................. 345

13.3.3.31 Switch Engine Port 1 Ingress Filtered Count Register (SWE_FILTERED_CNT_1) ..................................................................................... 346

13.3.3.32 Switch Engine Port 2 Ingress Filtered Count Register (SWE_FILTERED_CNT_2) ..................................................................................... 347

13.3.3.33 Switch Engine Port 0 Ingress VLAN Priority Regeneration Table Register (SWE_INGRSS_REGEN_TBL_MII) ........................................ 348

13.3.3.34 Switch Engine Port 1 Ingress VLAN Priority Regeneration Table Register (SWE_INGRSS_REGEN_TBL_1) ........................................... 349

13.3.3.35 Switch Engine Port 2 Ingress VLAN Priority Regeneration Table Register (SWE_INGRSS_REGEN_TBL_2) ........................................... 350

13.3.3.36 Switch Engine Port 0 Learn Discard Count Register (SWE_LRN_DISCRD_CNT_MII) ............................................................................... 351

13.3.3.37 Switch Engine Port 1 Learn Discard Count Register (SWE_LRN_DISCRD_CNT_1) .................................................................................. 352

13.3.3.38 Switch Engine Port 2 Learn Discard Count Register (SWE_LRN_DISCRD_CNT_2) .................................................................................. 353

13.3.3.39 Switch Engine Interrupt Mask Register (SWE_IMR)..................................................................................................................................... 354

13.3.3.40 Switch Engine Interrupt Pending Register (SWE_IPR)................................................................................................................................. 355

13.3.4 Buffer Manager CSRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

13.3.4.1

13.3.4.2

13.3.4.3

13.3.4.4

13.3.4.5

13.3.4.6

13.3.4.7

13.3.4.8

13.3.4.9

Buffer Manager Configuration Register (BM_CFG)...................................................................................................................................... 357

Buffer Manager Drop Level Register (BM_DROP_LVL)............................................................................................................................... 358

Buffer Manager Flow Control Pause Level Register (BM_FC_PAUSE_LVL)............................................................................................... 359

Buffer Manager Flow Control Resume Level Register (BM_FC_RESUME_LVL) ........................................................................................ 360

Buffer Manager Broadcast Buffer Level Register (BM_BCST_LVL)............................................................................................................. 361

Buffer Manager Port 0 Drop Count Register (BM_DRP_CNT_SRC_MII) .................................................................................................... 362

Buffer Manager Port 1 Drop Count Register (BM_DRP_CNT_SRC_1) ....................................................................................................... 363

Buffer Manager Port 2 Drop Count Register (BM_DRP_CNT_SRC_2) ....................................................................................................... 364

Buffer Manager Reset Status Register (BM_RST_STS) .............................................................................................................................. 365

13.3.4.10 Buffer Manager Random Discard Table Command Register (BM_RNDM_DSCRD_TBL_CMD) ................................................................ 366

13.3.4.11 Buffer Manager Random Discard Table Write Data Register (BM_RNDM_DSCRD_TBL_WDATA)........................................................... 367

13.3.4.12 Buffer Manager Random Discard Table Read Data Register (BM_RNDM_DSCRD_TBL_RDATA)............................................................ 368

13.3.4.13 Buffer Manager Egress Port Type Register (BM_EGRSS_PORT_TYPE) ................................................................................................... 369

13.3.4.14 Buffer Manager Port 0 Egress Rate Priority Queue 0/1 Register (BM_EGRSS_RATE_00_01) .................................................................. 371

13.3.4.15 Buffer Manager Port 0 Egress Rate Priority Queue 2/3 Register (BM_EGRSS_RATE_02_03) .................................................................. 372

13.3.4.16 Buffer Manager Port 1 Egress Rate Priority Queue 0/1 Register (BM_EGRSS_RATE_10_11) .................................................................. 373

13.3.4.17 Buffer Manager Port 1 Egress Rate Priority Queue 2/3 Register (BM_EGRSS_RATE_12_13) .................................................................. 374

13.3.4.18 Buffer Manager Port 2 Egress Rate Priority Queue 0/1 Register (BM_EGRSS_RATE_20_21) .................................................................. 375

13.3.4.19 Buffer Manager Port 2 Egress Rate Priority Queue 2/3 Register (BM_EGRSS_RATE_22_23) .................................................................. 376

13.3.4.20 Buffer Manager Port 0 Default VLAN ID and Priority Register (BM_VLAN_MII) .......................................................................................... 377

13.3.4.21 Buffer Manager Port 1 Default VLAN ID and Priority Register (BM_VLAN_1) ............................................................................................. 378

13.3.4.22 Buffer Manager Port 2 Default VLAN ID and Priority Register (BM_VLAN_2) ............................................................................................. 379

13.3.4.23 Buffer Manager Port 0 Ingress Rate Drop Count Register (BM_RATE_DRP_CNT_SRC_MII) ................................................................... 380

13.3.4.24 Buffer Manager Port 1 Ingress Rate Drop Count Register (BM_RATE_DRP_CNT_SRC_1) ...................................................................... 381

13.3.4.25 Buffer Manager Port 2 Ingress Rate Drop Count Register (BM_RATE_DRP_CNT_SRC_2) ...................................................................... 382

13.3.4.26 Buffer Manager Interrupt Mask Register (BM_IMR) ..................................................................................................................................... 383

13.3.4.27 Buffer Manager Interrupt Pending Register (BM_IPR) ................................................................................................................................. 384

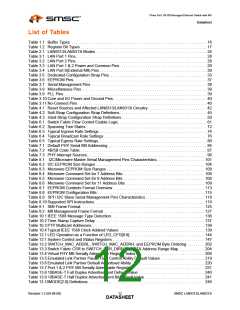

Chapter 14 Operational Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386

14.1 Absolute Maximum Ratings*. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386

14.2 Operating Conditions** . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386

14.3 Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 387

14.4 DC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 388

14.5 AC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 389

14.5.1 Equivalent Test Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 389

14.5.2 Reset and Configuration Strap Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 390

14.5.3 Power-On Configuration Strap Valid Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

14.5.4 Microwire Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

14.5.5 SPI Slave Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393

14.6 Clock Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

Chapter 15 Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

15.1 128-VTQFP Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

15.2 128-XVTQFP Package Outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 397

SMSC LAN9313/LAN9313i

9

Revision 1.2 (04-08-08)

DATASHEET

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]