Three Port 10/100 Managed Ethernet Switch with MII

Datasheet

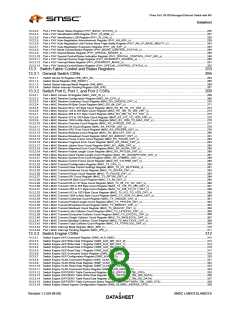

12.2.2.2

IEEE 1588 GPIO Interrupts........................................................................................................................................................................... 144

12.3 LED Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Chapter 13 Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

13.1 System Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

13.1.1 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

13.1.1.1

13.1.1.2

13.1.1.3

Interrupt Configuration Register (IRQ_CFG) ................................................................................................................................................ 151

Interrupt Status Register (INT_STS)............................................................................................................................................................. 153

Interrupt Enable Register (INT_EN).............................................................................................................................................................. 154

13.1.2 GPIO/LED. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

13.1.2.1

13.1.2.2

13.1.2.3

13.1.2.4

General Purpose I/O Configuration Register (GPIO_CFG) .......................................................................................................................... 155

General Purpose I/O Data & Direction Register (GPIO_DATA_DIR) ........................................................................................................... 157

General Purpose I/O Interrupt Status and Enable Register (GPIO_INT_STS_EN)...................................................................................... 158

LED Configuration Register (LED_CFG) ...................................................................................................................................................... 159

13.1.3 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

13.1.3.1

13.1.3.2

EEPROM Command Register (E2P_CMD).................................................................................................................................................. 160

EEPROM Data Register (E2P_DATA).......................................................................................................................................................... 163

13.1.4 IEEE 1588 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

13.1.4.1

13.1.4.2

13.1.4.3

13.1.4.4

13.1.4.5

13.1.4.6

13.1.4.7

13.1.4.8

13.1.4.9

Port x 1588 Clock High-DWORD Receive Capture Register (1588_CLOCK_HI_RX_CAPTURE_x) .......................................................... 164

Port x 1588 Clock Low-DWORD Receive Capture Register (1588_CLOCK_LO_RX_CAPTURE_x).......................................................... 165

Port x 1588 Sequence ID, Source UUID High-WORD Receive Capture Register (1588_SEQ_ID_SRC_UUID_HI_RX_CAPTURE_x)..... 166

Port x 1588 Source UUID Low-DWORD Receive Capture Register (1588_SRC_UUID_LO_RX_CAPTURE_x)........................................ 167

Port x 1588 Clock High-DWORD Transmit Capture Register (1588_CLOCK_HI_TX_CAPTURE_x).......................................................... 168

Port x 1588 Clock Low-DWORD Transmit Capture Register (1588_CLOCK_LO_TX_CAPTURE_x) ......................................................... 169

Port x 1588 Sequence ID, Source UUID High-WORD Transmit Capture Register (1588_SEQ_ID_SRC_UUID_HI_TX_CAPTURE_x) .... 170

Port x 1588 Source UUID Low-DWORD Transmit Capture Register (1588_SRC_UUID_LO_TX_CAPTURE_x) ....................................... 171

GPIO 8 1588 Clock High-DWORD Capture Register (1588_CLOCK_HI_CAPTURE_GPIO_8).................................................................. 172

13.1.4.10 GPIO 8 1588 Clock Low-DWORD Capture Register (1588_CLOCK_LO_CAPTURE_GPIO_8) ................................................................. 173

13.1.4.11 GPIO 9 1588 Clock High-DWORD Capture Register (1588_CLOCK_HI_CAPTURE_GPIO_9).................................................................. 174

13.1.4.12 GPIO 9 1588 Clock Low-DWORD Capture Register (1588_CLOCK_LO_CAPTURE_GPIO_9) ................................................................. 175

13.1.4.13 1588 Clock High-DWORD Register (1588_CLOCK_HI)............................................................................................................................... 176

13.1.4.14 1588 Clock Low-DWORD Register (1588_CLOCK_LO) .............................................................................................................................. 177

13.1.4.15 1588 Clock Addend Register (1588_CLOCK_ADDEND) ............................................................................................................................. 178

13.1.4.16 1588 Clock Target High-DWORD Register (1588_CLOCK_TARGET_HI)................................................................................................... 179

13.1.4.17 1588 Clock Target Low-DWORD Register (1588_CLOCK_TARGET_LO) .................................................................................................. 180

13.1.4.18 1588 Clock Target Reload High-DWORD Register (1588_CLOCK_TARGET_RELOAD_HI) ..................................................................... 181

13.1.4.19 1588 Clock Target Reload/Add Low-DWORD Register (1588_CLOCK_TARGET_RELOAD_LO).............................................................. 182

13.1.4.20 1588 Auxiliary MAC Address High-WORD Register (1588_AUX_MAC_HI) ................................................................................................ 183

13.1.4.21 1588 Auxiliary MAC Address Low-DWORD Register (1588_AUX_MAC_LO) ............................................................................................. 184

13.1.4.22 1588 Configuration Register (1588_CONFIG).............................................................................................................................................. 185

13.1.4.23 1588 Interrupt Status and Enable Register (1588_INT_STS_EN)................................................................................................................ 189

13.1.4.24 1588 Command Register (1588_CMD) ........................................................................................................................................................ 191

13.1.5 Switch Fabric . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

13.1.5.1

13.1.5.2

13.1.5.3

13.1.5.4

13.1.5.5

13.1.5.6

13.1.5.7

13.1.5.8

Port 1 Manual Flow Control Register (MANUAL_FC_1)............................................................................................................................... 192

Port 2 Manual Flow Control Register (MANUAL_FC_2)............................................................................................................................... 194

Port 0(External MII) Manual Flow Control Register (MANUAL_FC_MII) ...................................................................................................... 196

Switch Fabric CSR Interface Data Register (SWITCH_CSR_DATA)........................................................................................................... 198

Switch Fabric CSR Interface Command Register (SWITCH_CSR_CMD) ................................................................................................... 199

Switch Fabric MAC Address High Register (SWITCH_MAC_ADDRH)........................................................................................................ 201

Switch Fabric MAC Address Low Register (SWITCH_MAC_ADDRL) ......................................................................................................... 202

Switch Fabric CSR Interface Direct Data Register (SWITCH_CSR_DIRECT_DATA) ................................................................................. 204

13.1.6 PHY Management Interface (PMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

13.1.6.1

13.1.6.2

PHY Management Interface Data Register (PMI_DATA) ............................................................................................................................. 207

PHY Management Interface Access Register (PMI_ACCESS).................................................................................................................... 208

13.1.7 Virtual PHY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

13.1.7.1

13.1.7.2

13.1.7.3

13.1.7.4

13.1.7.5

13.1.7.6

13.1.7.7

13.1.7.8

Virtual PHY Basic Control Register (VPHY_BASIC_CTRL) ......................................................................................................................... 210

Virtual PHY Basic Status Register (VPHY_BASIC_STATUS)...................................................................................................................... 212

Virtual PHY Identification MSB Register (VPHY_ID_MSB) .......................................................................................................................... 214

Virtual PHY Identification LSB Register (VPHY_ID_LSB) ............................................................................................................................ 215

Virtual PHY Auto-Negotiation Advertisement Register (VPHY_AN_ADV).................................................................................................... 216

Virtual PHY Auto-Negotiation Link Partner Base Page Ability Register (VPHY_AN_LP_BASE_ABILITY).................................................. 218

Virtual PHY Auto-Negotiation Expansion Register (VPHY_AN_EXP).......................................................................................................... 221

Virtual PHY Special Control/Status Register (VPHY_SPECIAL_CONTROL_STATUS) .............................................................................. 222

13.1.8 Miscellaneous. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

13.1.8.1

13.1.8.2

13.1.8.3

13.1.8.4

13.1.8.5

13.1.8.6

13.1.8.7

Chip ID and Revision (ID_REV).................................................................................................................................................................... 224

Byte Order Test Register (BYTE_TEST) ...................................................................................................................................................... 225

Hardware Configuration Register (HW_CFG)............................................................................................................................................... 226

General Purpose Timer Configuration Register (GPT_CFG) ....................................................................................................................... 227

General Purpose Timer Count Register (GPT_CNT) ................................................................................................................................... 228

Free Running 25MHz Counter Register (FREE_RUN)................................................................................................................................. 229

Reset Control Register (RESET_CTL) ......................................................................................................................................................... 230

13.2 Ethernet PHY Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

13.2.1 Virtual PHY Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

13.2.2 Port 1 & 2 PHY Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

13.2.2.1

Port x PHY Basic Control Register (PHY_BASIC_CONTROL_x) ................................................................................................................ 233

SMSC LAN9313/LAN9313i

7

Revision 1.2 (04-08-08)

DATASHEET

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]