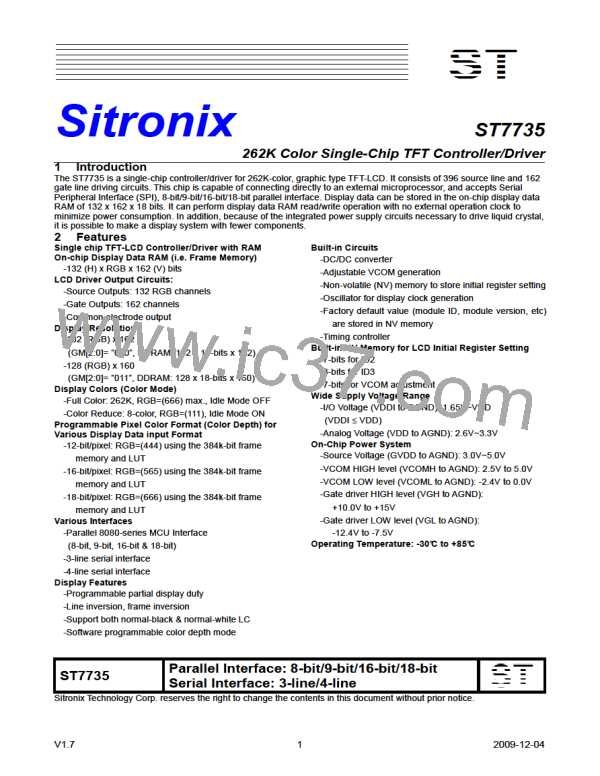

ST7735

10.1.26 MADCTL (36h): Memory Data Access Control

36H

Inst / Para

MADCTL

Parameter

MADCTL (Memory Data Access Control)

D/CX

WRX

RDX

D17-8 D7

D6

0

D5

1

D4

1

D3

0

D2

1

D1

1

D0

0

HEX

0

1

↑

↑

1

1

-

-

0

(36h)

MY

MX

MV

ML

RGB

MH

-

-

-This command defines read/ write scanning direction of frame memory.

Bit

NAME

DESCRIPTION

MY

MX

MV

Row Address Order

Column Address Order

Row/Column Exchange

These 3bits controls MCU to memory

write/read direction.

LCD vertical refresh direction control

‘0’ = LCD vertical refresh Top to Bottom

‘1’ = LCD vertical refresh Bottom to Top

Color selector switch control

ML

Vertical Refresh Order

RGB-BGR ORDER

RGB

MH

‘0’ =RGB color filter panel,

‘1’ =BGR color filter panel)

LCD horizontal refresh direction control

‘0’ = LCD horizontal refresh Left to right

‘1’ = LCD horizontal refresh right to left

Horizontal Refresh Order

-Bit Assignment

Top-left (0, 0)

Top-left (0, 0)

Memory

Display

Send first

Send 2nd

Send 3rd

ML="0"

Description

Send last

Top-left (0, 0)

ML="1"

Top-left (0, 0)

Memory

Display

Send last

Send 3rd

Send 2nd

Send first

RGB="0"

Driver IC

RGB="1"

Driver IC

R

G

B

R

G

B

R

G

B

R

G

B

R

G

B

R

G

B

SIG1

SIG2

SIG132

SIG1

SIG2

SIG132

SIG1

G

SIG2

G

SIG132

G

SIG1

G

SIG2

G

SIG132

G

R

R

B

B

R

R

B

B

R

R

B

B

B

B

R

R

B

B

R

R

B

B

R

R

G

G

G

G

G

G

LCD panel

LCD panel

V1.7

109

2009-12-04

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]

SITRONIX [ SITRONIX TECHNOLOGY CO., LTD. ]