SC9821C

(Continued)

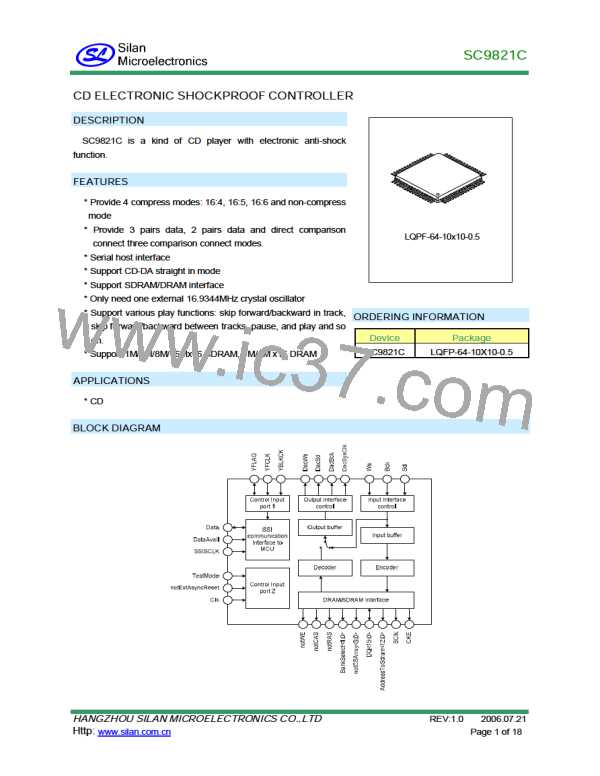

Symbol

Address

R/W

RW

Initialization

Description

Store the page base address (Bit1ˉ5Bit8) of

compare & connect data.

CompareDataBaseAd

dressHigh [7:0]

0x02

XX

Store the page base address (Bˉit7Bit0) of

compare & connect data.

CompareDataBaseAd

dressLow [7:0]

0x03

0x04

0x05

RW

RW

RW

XX

XX

XX

Store the page base address (Bit1ˉ5Bit8) of

G722 status data.

G722StatusBaseAddr

essHigh [7:0]

Store the page base address (Bˉit7Bit0) of

G722 status data.

G722StatusBaseAddr

essLow [7:0]

4. Program Guide

4.1 Enter Esp mode

First send short command 0x04, then enter Esp mode.

4.2 Configure external Sdram

HOST need to initialize Sdram. Send the command 0x51 0x52 0x52 0x53 0x54 0x50 0x58 to register

MmuHostCmd(8’h00) in turn.

Host initialized Dram. Send the command 0x47 to register MmuHostCmd(8’h00)

HOST need to configure the address of comparative data and decoding information. Send the command

0x0f to register CompareDataBaseAddressHigh(8’h02) , send the command 0xf4 to register

CompareDataBaseAddressLow (8’h03), send the command 0x0f to register

G722StatusBaseAddressHigh(8’h04) and send the command 0xf8 to register

G722StatusBaseAddressLow (8’h05).

HOST need to configure the size of Sdram. Now it can only support page as unit,

BitPoolPageLimitHigh(8’h58) BitPoolPageLimitLow(8’h59) .

4.3 Configure audio input and output interface.

HOST need to configure audio input interface. The input and output are 24 Bitclk of IIS interface. Send

the command 0x0f to register BitStreamType (8’h76).

4.4 Configure compress mode, shake detecting mode, and shake signal shield time.

HOST need to configure the compress mode. There are 4 compress modes to be selected (16: 4

compress, 16:5 compress, 16:6 compress and non•compress), which will send the command to register

MSC85H(8’h52).

HOST need to configure the shake detecting mode. There are 4 modes to be detected(rising edge of sub

block sync signal, shake signal low level determinant; falling edge of sub block sync signal, shake signal

high level determinant; shake signal low level determinant; shake signal high level determinant), Send

the command to register MSC85H(8’h52).

HOST can configure shake signal shield time. Because Cd servo only receives some very short level

jam signal, but not the signal we need, we can solve this problem by setting the shake signal shield time.

HANGZHOU SILAN MICROELECTRONICS CO.,LTD

Http:

REV:1.0

2006.07.21

www.silan.com.cn

Page 15 of 18

SILAN [ SILAN MICROELECTRONICS JOINT-STOCK ]

SILAN [ SILAN MICROELECTRONICS JOINT-STOCK ]