SK4404

Quad Buffer/Receiver

HIGH-PERFORMANCE PRODUCTS

Description

ꢀeatures

The SK4404 is an extremely fast, stable and accurate

low skew quad buffer or cable driver / receiver. It can

asychronously pass four distinct signals, or it can

resynchronize them to a common clock. In addition, all

four outputs may be asynchronously enabled or

disabled. All of the D flip-flops are triggered on the

rising edge of the CLK input.

•

Quad Buffer/Driver

3 GHz Fmax

3.3V / 5.2V Compatible

Available in 32 lead, 5mm X5mm, TQFP

Package

•

•

•

Application Notes

AN1001 - EPIC Family Product Line

AN1003 - Termination Techniques for ECL / LVECL

PECL / LVPECL Devices

AN1004 - Interfacing Between LVDS and ECL /

LVECL / PECL / LVPECL

The SK4404 uses 50Ω outputs with sink/source

capability, and is optimized for applications that require:

• Point to point, double terminated, timing

critical lines

• Point to point, series terminated, timing

critical lines

Input Options

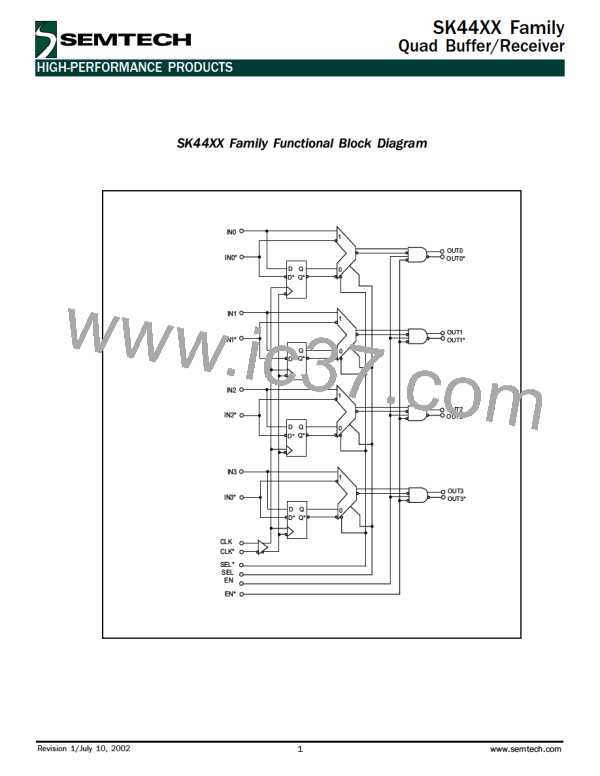

ꢀunctional Block Diagram

Open

IN<0 - 3>

IN0

1

OUT0

IN0*

OUT0*

IN<0 - 3>*

D

Q

0

D* Q*

Output Options

IN1

1

0

OUT1

50Ω Source / Sink

OUT1*

IN1*

D

Q

Q*

D*

VCC

IN2

1

0

50Ω

50Ω

OUT2

IN2*

OUT

OUT

OUT2*

Q

D

Q*

D*

*

10 mA

10 mA

IN3

VEE

1

0

VEE

OUT3

IN3*

OUT3*

D

Q

Q*

D*

CLK

Pin Description

CLK*

SEL*

SEL

EN

EN*

VCC

VCC

OUT1*

OUT1

SEL

SEL*

Package Information

V

V

EE

EE

CLK*

CLK

OUT2

EN

OUT2*

EN*

32 pin, 5 mm X 5 mm

V

CC

V

CC

TQFP Package

Revision 1/July 10, 2002

www.semtech.com

10

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]