SC4905A/B

POWER MANAGEMENT

PRELIMINARY

Application Information (Cont.)

VDD UNDER VOLTAGE LOCK OUT

According to the application, and the voltages available,

the SC4905A (UVLO = 4.5V), or the SC4905B (UVLO =

12.5V) can be used to provide the VDD undervoltage lock

out function to ensure the converters controlled start up.

Before the VDD UVLO has been reached, the internal ref-

erence, oscillator, OUT driver, and logic are disabled.

Following equation can be used to calculate the oscilla-

tor frequency:

VFF

Vin −

2

FOSC

≅

R

(

• C

• VFF•1.05

)

OSC

OSC

REFERENCE

The recommended range if timing resistors is between 10

kohm and 500kohm and range of timing capacitors is

between 100pF and 1000pF. Timing resistors less than

10 kohm should be avoided.

A 4V (SC4905A) or a 5V(SC4905B) reference voltage is

available that can be used to source a typical current of

3mA to the external circuitry. The REF can be used to

provide the feed back circuitry with a regulated bias.

OSCILLATOR

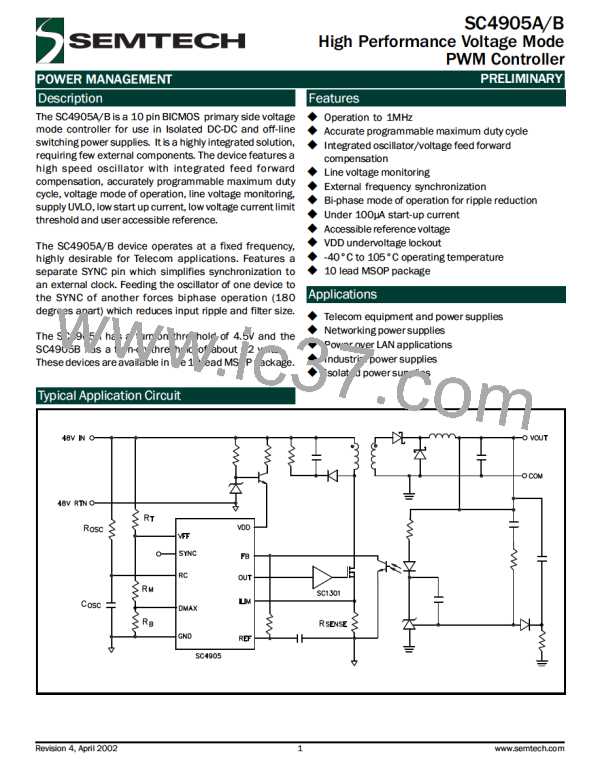

The oscillator frequency is set by connecting a RC network

as shown below.

Vin

SC4905

U1

1

2

3

4

5

10

9

VDD

FB

REF

OUT

RT

280k

Rosc

499k

8

VFF

DMAX

RC

GND

ILIM

7

RM

2k

6

SYNC

RB

Cosc

8.25k

220p, 16V

The oscillator has a ramp voltage that will track the volt-

age at the VFF pin (1.2V<VFF<3.6V). The oscillator peak

voltage is derived by charging the oscillator capacitor (Cosc)

to the VFF voltage via the oscillator resistor (Rosc). The

bias current to charge the Cosc is controlled by the Rosc.

Once the RC pin has reached the VFF voltage, the oscil-

lator ramp is discharged by an internal switch hence cre-

ating the triangle oscillator ramp.

Since the Rosc is referenced to the input supply volt-

age, any variation in the supply is directly translated into

a variation in the duty cycle, while maintaining the fixed

frequency operation.

2002 Semtech Corp.

8

www.semtech.com

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]