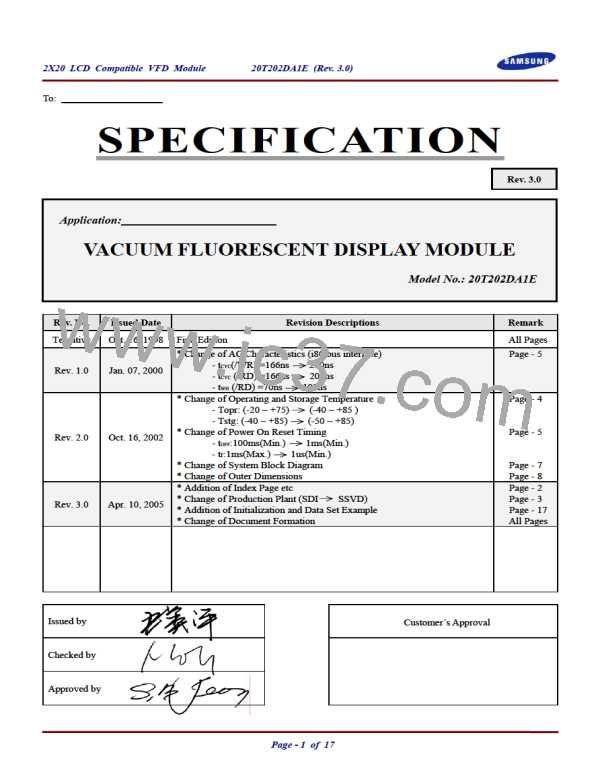

2X20 LCD Compatible VFD Module

20T202DA1E (Rev. 3.0)

4.7 Timing Chart and AC Characteristics

4.7.1 Power-on Reset Timing

tOFF(VCC)

1ms/Min.

VCC

tr(VCC)

1us/Min.

/WR

tWAIT (*)

t/RST

100us/Min.

500ns/Min.

/RST

(*) Note-2: Internal Reset Timing Interval

Fig.-1. Power-on Reset and /RST Signal Timing

4.7.2 M68 type CPU Bus Interface Timing

tH (RS,R/W)

10ns/Min.

tSU(RS,/R/W)

20ns/Min.

R/W

RS

E

tCYC(E)

500ns/Min.

tWH (E)

230ns/Min.

TWL (E)

230ns/Min.

tSU (DATA)

80ns/Min.

tH (DATA)

10ns/Min.

Valid Data Input

DB0~DB7

Fig.-2. Data Write-in Timing for M68 Interface Mode

tH (RS,R/W)

R/W

RS

E

tSU(RS,/R/W)

20ns/Min.

10ns/Min.

tCYC(E)

500ns/Min.

tWH (E)

TWL (E)

230ns/Min.

230ns/Min.

TDELAY (DATA)

160ns/Max.

tH (DATA)

5ns/Min.

Effective Data Output

DB0~DB7

Fig.-3. Data Read-out Timing for M68 Interface Mode

Page - 5 of 17

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]