RT8802A

Applications Information

MOSFETs. After VDD, VTT/EN, and DVD are ready,

RT8802A initiates its soft start cycle that is compliant

with Intel®VRD11 specification as shown in Figure 1. A

time variant internal current source charges the capacitor

connected to SS pin. SS voltage ramps up piecewise

linearly and locks VID_DAC output with a specified voltage

drop. Consequently, VCORE is built up according to

VID_DAC output and meet Intel® VRD11 requirement.

VR_READY output is pulled high by external resistor when

VCORE reaches VID_DAC output with 1~2ms delay. An

SS capacitor about 47nF is recommend for VRD11

compliance.

RT8802A is a multi-phase DC/DC controller specifically

designed to deliver high quality power for next generation

CPU. RT8802A controls a special power on sequence &

monitors the thermal condition of VR module to meet the

VRD11 requirement. Phase currents are sensed by

innovative time-sharing DCR current sensing technique

for channel current balance, droop tuning, and over current

protection. Using one common GM amplifier for current

sensing eliminates offset errors and linearity variation

between GMs. As sub-milli-ohm-grade inductors are

widely used in modern mother boards, slight mismatch

ofGM amplifiers offset and linearity results in considerable

current shift between phases. The time-sharing DCR

current sensing technique is extremely important to

guarantee phase current balance in mass production.

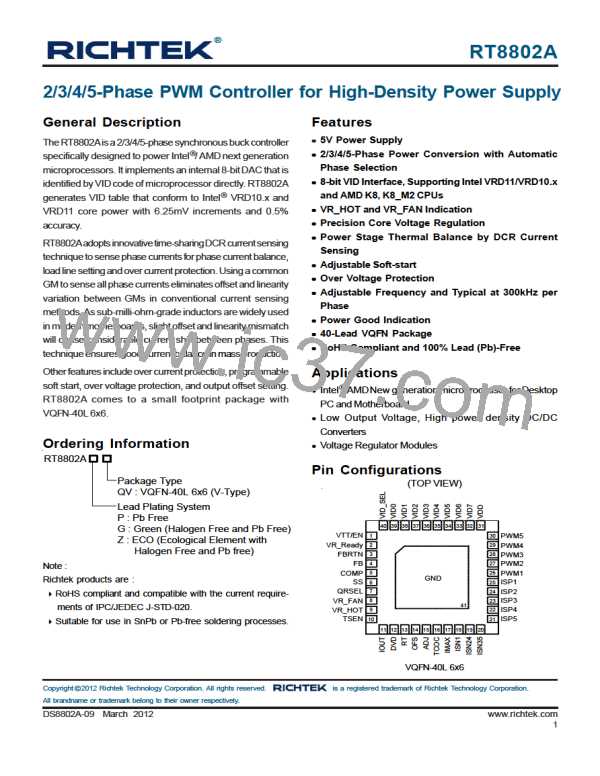

VDD POR, DVD, and VTT/EN ready

SS

VCORE

1.1V

Converter Initialization, Phase Selection, and

Power Good Function

VR_Ready

VID on the fly

The RT8802A initiates only after 3 pins are ready: VDD

pin power on reset (POR), VTT/ENpin enabled, andDVD

pin is higher than 1V. VDDPOR is to make sure RT8802A

is powered by a voltage for normal work. The rising

threshold voltage of VDD POR is 4.2V typically. At VDD

POR, RT8802Achecks PWM3, PWM4 and PWM5 status

to determine phase number of operation. Pull high PWM3

for two-phase operation; pull high PWM4 for three phase

operation; pull high PWM5 for four-phase operation. The

unused current sense pins should be connected to GND

or left floating.

1~2ms

1~2ms

1~2ms

1~2ms

1~2ms

Figure 1. TimingDiagramDuring Soft Start Interval

Voltage Control

CPU VCORE voltage is Kelvin sensed by FB and FBRTN

pins and precisely regulated to VID_DAC output by internal

high gain Error Amplifier (EA). The sensed signal is also

used for power good and over voltage function. The typical

OVP trip point is 170mV above VID_DAC output. RT8802A

pulls PWM outputs low and latches up upon OVP trip to

prevent damaging the CPU. It can only restart by resetting

one of VDD, DVD, or VTT/EN pin.

VTT/ENacts as a chip enable pin and receives signal from

FSB or other power management IC.

DVD is to make sure that ATX12V is ready for drivers to

work normally. Connect a voltage divider fromATX12V to

DVDpin as shown in the TypicalApplication Circuit. Make

sure that DVD pin voltage is below its threshold voltage

before drivers are ready and above its threshold voltage

for minimumATX12V during normal operation.

RT8802A supports Intel VRD10.x, VRD11, AMD K8 and

AMD K8_M2 VID specification.

The change of VID_DAC output at VID on the fly is also

smoothed by capacitor connected to SS pin.

Consequently, Vcore shifts to its new position smoothly

as shown in Figure 2.

If any one of VDD, VTT/EN, andDVDis not ready, RT8802A

keeps its PWM outputs high impedance and the

companion drivers turn off both upper and lower

Copyright 2012 Richtek Technology Corporation. All rights reserved.

©

is a registered trademark of Richtek Technology Corporation.

All brandname or trademark belong to their owner respectively.

www.richtek.com

22

DS8802A-09 March 2012

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]