3858 Group

CNTR

switch bit

3 active edge

Data bus

Programmable one-shot

“1”

“0”

generating mode

P43/INT2

Programmable one-shot

generating circuit

Programmable one-shot

generating mode

To INT2 interrupt

request bit

Programmable waveform

generating mode

D

T

Output level latch

Q

Pulse output mode

CNTR

3

active edge

switch bit

S

“0”

Q

Q

T

“1”

Pulse output mode

“001”

“100”

“101”

Timer Z2 operating

mode bits

Timer Z2 low-order latch Timer Z2 high-order latch

Timer Z2 low-order Timer Z2 high-order

To timer Z2 interrupt

request bit

Port P2

latch

3

Port P2

3

direction register

Pulse period measurement mode

Pulse width measurement mode

Edge detection circuit

To CNTR

3 interrupt

request bit

“1”

“0”

“1”

f(XCIN

)

P23/CNTR3

“0”

CNTR

switch bit

3 active edge

Timer Z2 count stop bit

Timer/Event

counter mode

switch bit

Clock for

timer Z2

X

IN

Count source

selection bit

Divider

(1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, 1/512, 1/1024)

X

CIN

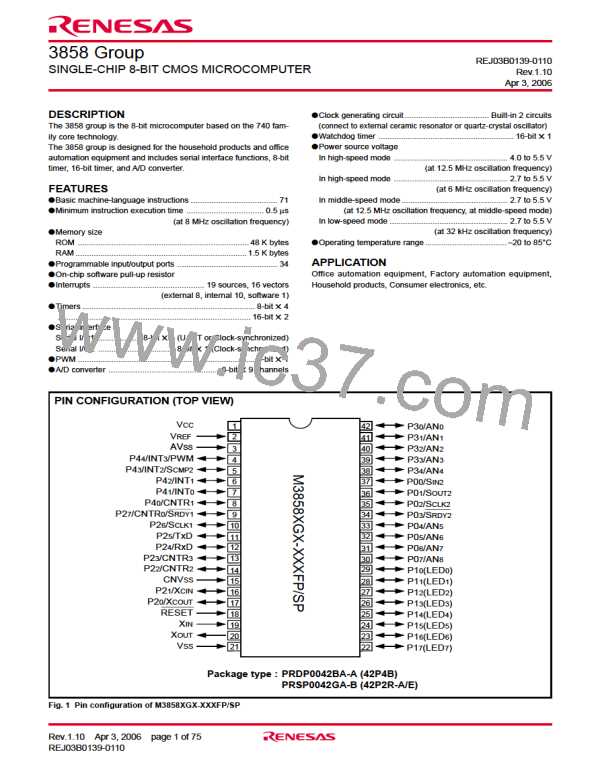

Fig. 28 Block diagram of timer Z2

Rev.1.10 Apr 3, 2006 page 38 of 75

REJ03B0139-0110

RENESAS [ RENESAS TECHNOLOGY CORP ]

RENESAS [ RENESAS TECHNOLOGY CORP ]