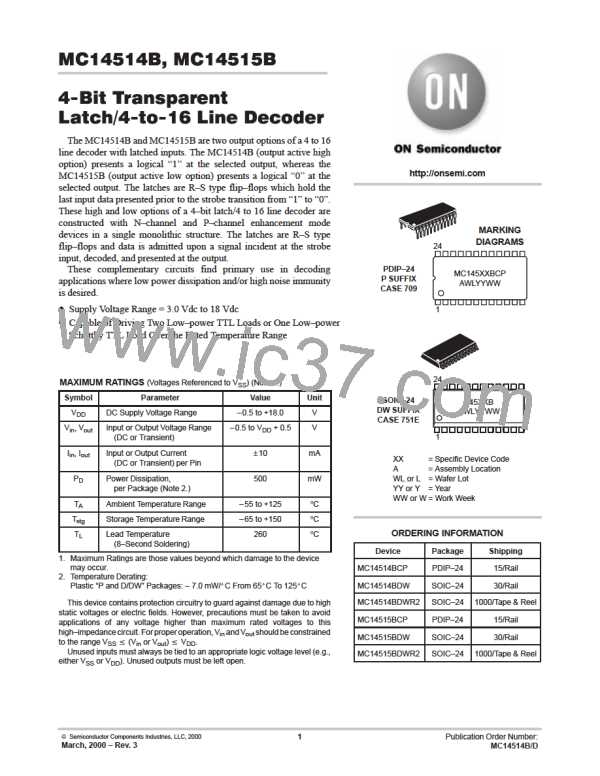

MC14514B, MC14515B

PIN ASSIGNMENT

ST

D1

D2

S7

S6

S5

1

2

3

4

5

6

24

V

DD

23 INH

22 D4

21 D3

20 S10

19 S11

S4

S3

S1

7

8

9

18 S8

17 S9

16 S14

15 S15

14 S12

13 S13

S2 10

S0 11

V

SS

12

DECODE TRUTH TABLE (Strobe = 1)*

Selected Output

Data Inputs

MC14514 = Logic “1”

MC14515 = Logic “0”

Inhibit

D

C

B

A

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

0

1

S0

S1

S2

S3

0

0

0

0

0

0

0

0

1

1

1

1

0

0

1

1

0

1

0

1

S4

S5

S6

S7

0

0

0

0

1

1

1

1

0

0

0

0

0

0

1

1

0

1

0

1

S8

S9

S10

S11

0

0

0

0

1

1

1

1

1

1

1

1

0

0

1

1

0

1

0

1

S12

S13

S14

S15

1

X

X

X

X

All Outputs = 0, MC14514

All Outputs = 1, MC14515

X = Don’t Care

*Strobe = 0, Data is latched

BLOCK DIAGRAM

11

S0

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

A B C D

9

S1

10

S2

V

V

SS

= PIN 24

= PIN 12

DD

8

S3

S4

7

6

2

3

A

B

C

D

S5

DATA 1

DATA 2

DATA 3

DATA 4

5

S6

S7

4

TRANSPARENT

LATCH

4 TO 16

DECODER

18

17

21

22

S8

S9

20

S10

19

S11

S12

14

1

STROBE

13

S13

S14

16

15

S15

23

INHIBIT

http://onsemi.com

2

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]