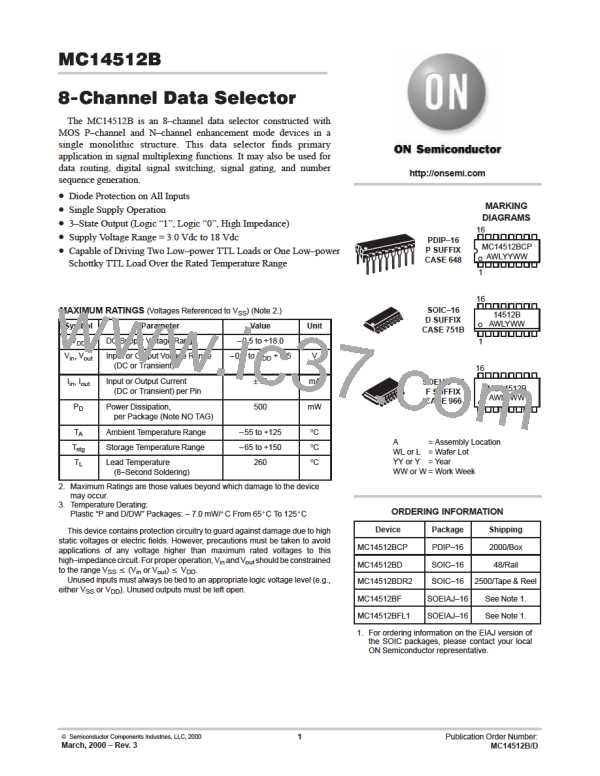

MC14512B

V

DD

20 ns

t

20 ns

DATA

V

DD

90%

DISABLE

INHIBIT

A

B

C

50%

10%

V

SS

Z

t

PLH

PHL

90%

50%

V

OH

C

L

Z

10%

V

OL

X0

X1

X2

X3

X4

X5

X6

X7

t

t

THL

TLH

PULSE

GENERATOR

TEST CONDITIONS:

INHIBIT = V

SS

A, B, C = V

SS

20 ns

INHIBIT,

A, B, OR C

20 ns

V

DD

90%

50%

10%

V

SS

t

t

PLH

PHL

V

SS

V

OH

90%

50%

10%

Parameter

Inhibit to Z

A, B, C to Z

Test Conditions

A, B, C = V , X = V

DD

Z

SS

O

V

OL

Inh = V , X = V

t

t

TLH

SS

O

DD

THL

Figure 2. AC Test Circuit and Waveforms

V

DD

20 ns

PULSE

GENERATOR

20 ns

V

DD

V

DD

90%

50%

10%

DISABLE

INHIBIT

A

V

DD

Z

DISABLE

INPUT

V

SS

C

L

S1

S2

V

B

C

X0

X1

X2

X3

t

1 k

PZL

V

t

PLZ

S3

S4

OH

90%

≈ 2.5 V @ V = 5 V,

10 V, AND 15 V

DD

10%

OUTPUT

OUTPUT

V

OL

t

t

PZH

PHZ

≈ 2 V @ V = 5 V

DD

V

SS

≈ 6 V @ V = 10 V

OH

DD

90%

X4

X5

X6

X7

10%

≈ 10 V @ V = 15 V

DD

V

SS

V

OL

Switch Positions for 3–State Test

Test

S1

S2

S3

S4

t

Open

Closed

Closed

Open

Closed Closed

Open

Closed

Closed

Open

PHZ

V

SS

t

t

Open

Open

Open

Open

PLZ

PZL

PZH

t

Closed Closed

Figure 3. 3–State AC Test Circuit and Waveform

http://onsemi.com

5

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]