MC10H166

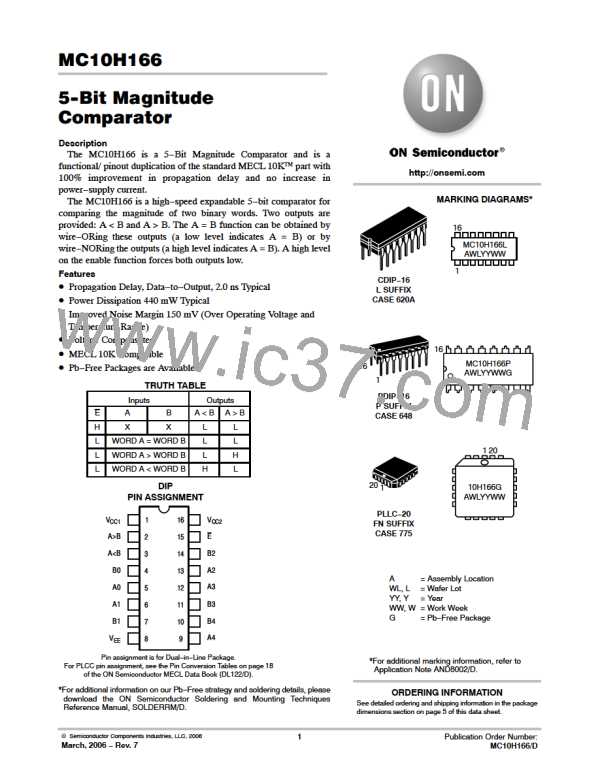

FIGURE 2 − 25−BIT MAGNITUDE COMPARATOR

B24

A24

B23

A23

B22

A22

B21

A21

B20

A20

B4

A4

B3

A3 A < B

B2

A2

B1

A > B

A1

B0

A0

B19

A19

B18

A18

B17

A17

B16

A16

B15

A15

B4

A4

B3

A < B

A3

B2

A2

A > B

B1

A1

B0

A0

B14

A14

B13

A13

B12

A12

B4

B4

A4

A = B

A4

B3

A3

B2

B3

A ꢃ

A < B

A3 A < B

B2

A2

B1

A1

B0

A0

B

A2

B1

B11

A ꢂ

A > B

A > B

A11

A10

B9

A1

B0

A0

B

B10

B4

A4

B3

A3

B2

A2

B1

A9

A8

A7

B8

B7

B6

B5

A

A

ꢃ B

ꢂ B

For shorter delay times than possible with serial expansion,

devices can be cascaded. Figure 2 shows a 25−bit cascaded

comparator whose worst case delay is two data−to−output delays.

The cascaded scheme can be extended to longer word lengths.

A6

A5

A1

B0

A0

B4

B3

B2

B1

B0

B4

A4

A3

A2

A4

B3

A3

B2

A2

A

B

ꢃ

B1

A1

B0

A0

A

ꢂ B

A1

A0

http://onsemi.com

4

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]