FEDL66517-01

1

Semiconductor

ML66517 Family

Slave mode (Clock synchronous serial port)

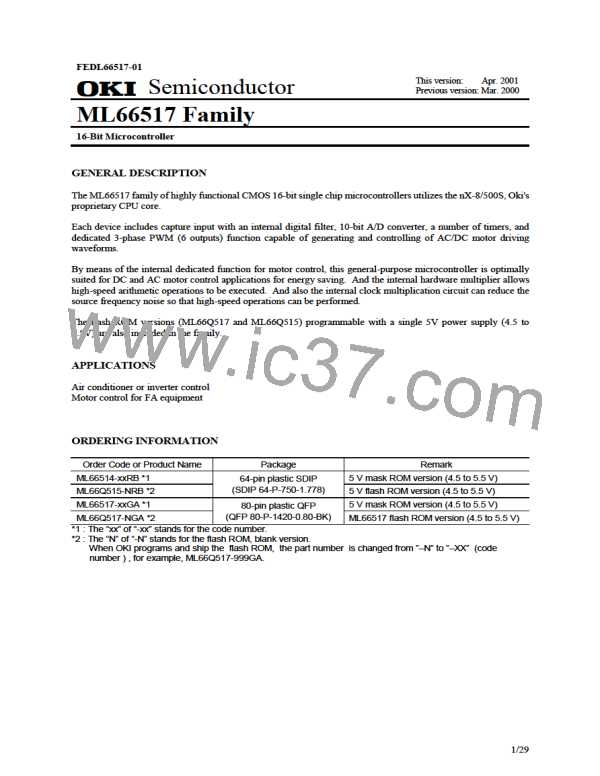

(VDD = 4.5 to 5.5 V, Ta = –40 to +85°C)

Parameter

Symbol

tcyc

Condition

Min.

40

Max.

—

Unit

Cycle time

fOSC = 25 MHz

Serial clock cycle time

Output data setup time

Output data hold time

Input data setup time

Input data hold time

tSCKC

4 tcyc

2tφ – 15

4tφ – 10

13

—

tSTMXS

tSTMXH

tSRMXS

tSRMXH

—

ns

CL = 50 pF

—

—

3

—

Note: tφ = tcyc/2

tcyc

CPUCLK

TXC/RXC

tSCKC

SDOUT

(TXD)

tSTMXH

tSTMXS

SDIN

(RXD)

tSRMXS

tSRMXH

Measurement points for AC timing (the serial port)

VDD

0.8VDD

0.2VDD

0.8VDD

0.2VDD

0 V

Measurement points for AC timing (except the serial port)

VDD

2.0 V

0.8 V

2.0 V

0.8 V

0 V

22/29

OKI [ OKI ELECTRONIC COMPONETS ]

OKI [ OKI ELECTRONIC COMPONETS ]