List of figures

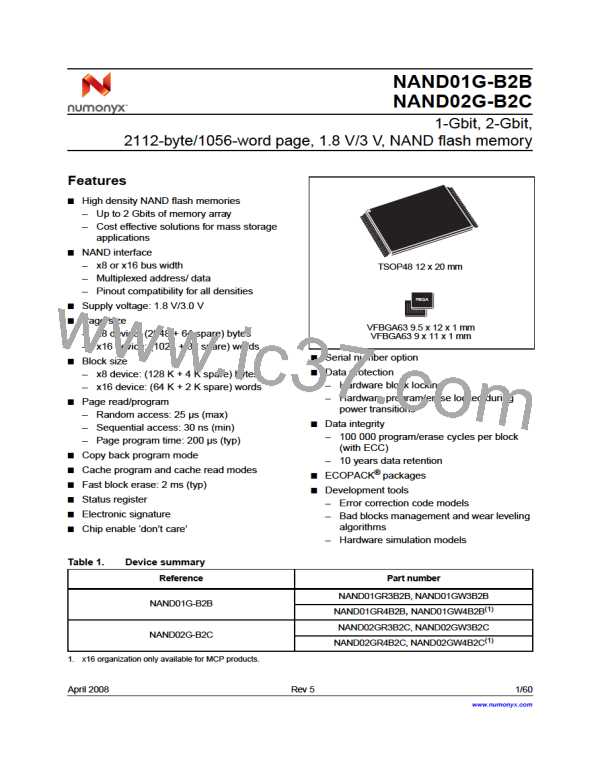

NAND01G-B2B, NAND02G-B2C

List of figures

Figure 1.

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

Logic block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

TSOP48 connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

VFBGA63 connections (top view through package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Memory array organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Read operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Random data output during sequential data output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Cache read operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Page program operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 10. Random data input during sequential data input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 11. Copy back program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 12. Page copy back program with random data input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 13. Cache program operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 14. Block erase operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 15. Bad block management flowchart. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 16. Garbage collection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 17. Error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 18. Equivalent testing circuit for AC characteristics measurement. . . . . . . . . . . . . . . . . . . . . . 42

Figure 19. Command latch AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 20. Address latch AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 21. Data Input Latch AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 22. Sequential data output after read AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 23. Read status register AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 24. Read electronic signature AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 25. Page read operation AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 26. Page program AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 27. Block erase AC waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 28. Reset AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 29. Program/erase enable waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 30. Program/erase disable waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 31. Ready/Busy AC waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 32. Ready/Busy load circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 33. Resistor value versus waveform timings for Ready/Busy signal. . . . . . . . . . . . . . . . . . . . . 54

Figure 34. Data protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 35. TSOP48 - 48 lead plastic thin small outline, 12 x 20 mm, package outline . . . . . . . . . . . . 55

Figure 36. VFBGA63 9.5 x 12 mm - 6 x 8 active ball array, 0.80 mm pitch, package outline . . . . . . . 56

Figure 37. VFBGA63 9 x 11 mm - 6 x 8 active ball array, 0.80 mm pitch, package outline. . . . . . . . . 57

6/60

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]