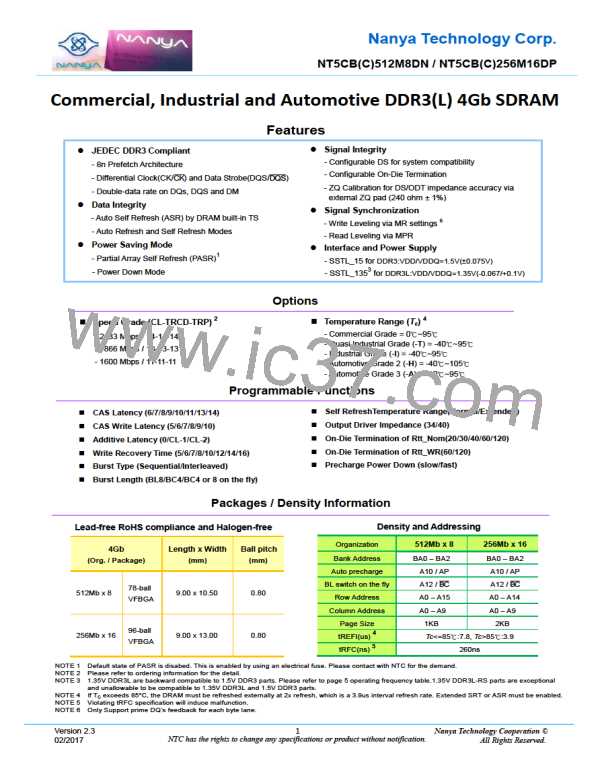

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

command must be registered (with tIS set up time to clock) before CKE goes active. Once the CKE registered “High”

after Reset, CKE needs to be continuously registered “High” until the initialization sequence is finished, including expi-

ration of tDLLK and tZQinit

.

4. The DDR3(L) DRAM will keep its on-die termination in high impedance state as long as REETis asserted. Further,

the DRAM keeps its on-die termination in high impedance state after REET de-assertion until CKE is registered HIGH.

The ODT input signal may be in undefined state until tIS before CKE is registered HIGH. When CKE is registered

HIGH, the ODT input signal may be statically held at either LOW or HIGH. If RTT_NOM is to be enabled in MR1, the

ODT input signal must be statically held LOW. In all cases, the ODT input signal remains static until the power up

initialization sequence is finished, including the expiration of tDLLK and tZQinit.

5. After CKE being registered high, wait minimum of Reset CKE Exit time, tXPR, before issuing the first MRS command

to load mode register. [TXPR=max (tXS, 5tCK)]

6. Issue MRS command to load MR2 with all application settings. (To issue MRS command for MR2, provide “Low” to

BA0 and BA2, “High” to BA1)

7. Issue MRS command to load MR3 with all application settings. (To issue MRS command for MR3, provide “Low” to

BA2, “High” to BA0 and BA1)

8. Issue MRS Command to load MR1 with all application settings and DLL enabled. (To issue “DLL Enable” command,

provide “Low” to A0, “High” to BA0 and “Low” to BA1 and BA2)

9. Issue MRS Command to load MR0 with all application settings and “DLL reset”. (To issue DLL reset command,

provide “High” to A8 and “Low” to BA0-BA2)

10. Issue ZQCL command to starting ZQ calibration.

11. Wait for both tDLLK and tZQinit completed.

12. The DDR3 (L) SDRAM is now ready for normal operation.

Version 2.3

02/2017

13

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]