MITSUBISHI MICROCOMPUTERS

3822 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Timer X

ꢀReal time port control

Timer X is a 16-bit timer that can be selected in one of four modes

and can be controlled the timer X write and the real time port by

setting the timer X mode register.

While the real time port function is valid, data for the real time port

are output from ports P52 and P53 each time the timer X

underflows. (However, after rewriting a data for real time port, if

the real time port control bit is changed from “0” to “1”, data are

output independent of the timer X operation.) If the data for the

real time port is changed while the real time port function is valid,

the changed data are output at the next underflow of timer X.

Before using this function, set the corresponding port direction

registers to output mode.

(1) Timer Mode

The timer counts f(XIN)/16 (or f(XCIN)/16 in low-speed mode).

(2) Pulse Output Mode

Each time the timer underflows, a signal output from the CNTR0

pin is inverted. Except for this, the operation in pulse output mode

is the same as in timer mode. When using a timer in this mode,

set the corresponding port P54 direction register to output mode.

ꢀNote on CNTR0 interrupt active edge

selection

CNTR0 interrupt active edge depends on the CNTR0 active edge

(3) Event Counter Mode

switch bit.

The timer counts signals input through the CNTR0 pin.

Except for this, the operation in event counter mode is the same

as in timer mode. When using a timer in this mode, set the corre-

sponding port P54 direction register to input mode.

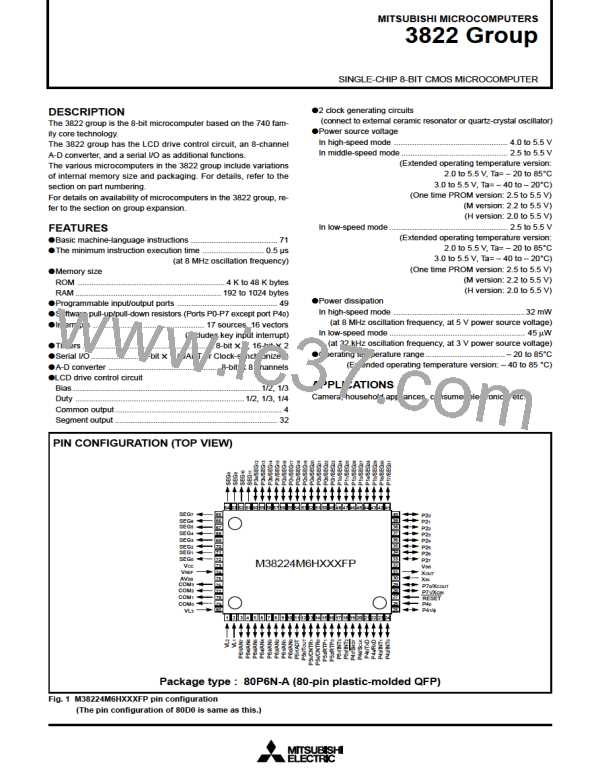

b7

b0

Timer X mode register

(TXM : address 002716

)

(4) Pulse Width Measurement Mode

The count source is f(XIN)/16 (or f(XCIN)/16 in low-speed mode). If

CNTR0 active edge switch bit is “0”, the timer counts while the in-

put signal of CNTR0 pin is at “H”. If it is “1”, the timer counts while

the input signal of CNTR0 pin is at “L”. When using a timer in this

mode, set the corresponding port P54 direction register to input

mode.

Timer X write control bit

0 : Write value in latch and counter

1 : Write value in latch only

Real time port control bit

0 : Real time port function invalid

1 : Real time port function valid

P5

2

data for real time port

data for real time port

P53

Timer X operating mode bits

b5 b4

0

0

1

1

0 : Timer mode

1 : Pulse output mode

0 : Event counter mode

1 : Pulse width measurement mode

ꢀTimer X write control

If the timer X write control bit is “0”, when the value is written in the

address of timer X, the value is loaded in the timer X and the latch

at the same time.

CNTR0 active edge switch bit

0 : Count at rising edge in event counter mode

Start from “H” output in pulse output mode

Measure “H” pulse width in pulse width

measurement mode

If the timer X write control bit is “1”, when the value is written in the

address of timer X, the value is loaded only in the latch. The value

in the latch is loaded in timer X after timer X underflows.

If the value is written in latch only, when writing in the timer latch at

the timer underflow, the value is set in the timer and the latch at

one time. Additionally, unexpected value may be set in the high-or-

der counter when the writing in high-order latch and the underflow

of timer X are performed at the same timing.

Falling edge active for CNTR0 interrupt

1 : Count at falling edge in event counter mode

Start from “L” output in pulse output mode

Measure “L” pulse width in pulse width

measurement mode

Rising edge active for CNTR

Timer X stop control bit

0 : Count start

0 interrupt

1 : Count stop

Fig. 22 Structure of timer X mode register

26

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]