P R O D U C T D A T A B O O K 1 9 9 6 / 1 9 9 7

SG1842/SG1843 Series

C

U R R E N T - M O D E P W M C O N T R O L L E R

P R O D U C T I O N D A T A S H E E T

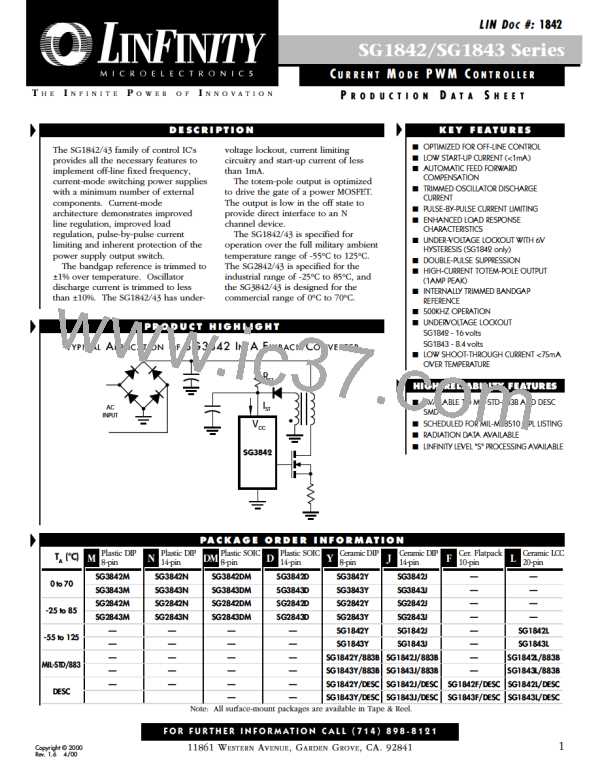

BLOCK DIAGRAM

VCC*

34V

UVLO

VREF

5.0V

50mA

5V

S / R

REF

GROUND**

6V (1842)

0.8V (1843)

16V (1842)

8.4V (1843)

INTERNAL

BIAS

2.5V

VREF

GOOD LOGIC

VC*

OSCILLATOR

ERROR AMP

R / CT

T

OUTPUT

S

2R

R

POWER GROUND**

1V

R

PWM

LATCH

VFB

COMP

CURRENT SENSE

COMPARATOR

CURRENT SENSE

- VCC and VC are internally connected for 8 pin packages.

- POWER GROUND and GROUND are internally connected for 8 pin packages.

*

**

Copyright © 2000

Rev. 1.6 4/00

5

MICROSEMI [ Microsemi ]

MICROSEMI [ Microsemi ]