ADVANCE

128Mb: x16, x32

MOBILE SDRAM

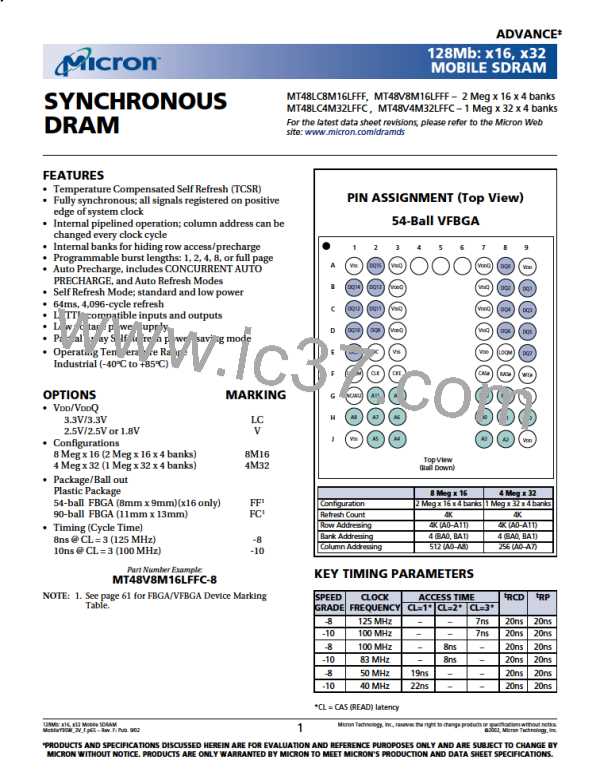

ALTERNATING BANK READ ACCESSES1

T0

T1

T2

T3

T4

T5

T6

T7

T8

t

CK

t

CL

CLK

t

CH

t

t

CKS

CKH

CKE

COMMAND

t

t

CMS

CMH

ACTIVE

NOP

READ

t

NOP

ACTIVE

NOP

READ

NOP

ACTIVE

t

CMS

CMH

DQMU, DQML

A0-A9, A11

t

t

AH

AS

2

2

ROW

ROW

ROW

ROW

COLUMN m

COLUMN b

t

AS

t

AH

ENABLE AUTO PRECHARGE

ENABLE AUTO PRECHARGE

ROW

ROW

A10

t

AS

t

AH

BA0, BA1

BANK 0

BANK 0

BANK 3

t

BANK 3

BANK 0

t

AC

t

t

AC

t

AC

AC

AC

t

AC

t

OH

t

OH

t

OH

t

OH

t

OH

DOUT

m

DOUT m + 1

DOUT m + 2

D

OUT m + 3

DOUT b

DQ

t

LZ

t

t

RCD - BANK 0

t

RCD - BANK 0

CAS Latency - BANK 0

RP - BANK 0

t

RAS - BANK 0

t

RC - BANK 0

t

t

RCD - BANK 3

CAS Latency - BANK 3

RRD

DON’T CARE

UNDEFINED

TIMING PARAMETERS

-8

-10

-8

-10

SYMBOL*

MIN

MAX

MIN

MAX UNITS

SYMBOL*

MIN

2.5

1

MAX

MIN

2.5

1

MAX UNITS

t

t

AC (3)

7

8

7

8

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

CKS

ns

ns

ns

ns

ns

t

t

AC (2)

CMH

t

t

AC (1)

19

22

CMS

2.5

1

2.5

1

t

t

AH

1

2.5

3

1

2.5

3

LZ

t

t

AS

OH

2.5

48

80

20

20

20

2.5

50

t

t

CH

RAS

120,000

120,000

ns

ns

ns

ns

ns

t

t

CL

3

3

RC

100

20

t

t

CK (3)

8

10

12

25

1

RCD

t

t

CK (2)

10

20

1

RP

20

t

t

CK (1)

RRD

20

t

CKH

*CAS latency indicated in parentheses.

NOTE: 1. For this example, the burst length = 4, and the CAS latency = 2.

2. x16: A9 and A11 = “Don’t Care”

x32: A8, A9,and A11 = “Don’t Care”

128Mb: x16, x32 Mobile SDRAM

MobileY95W_3V_F.p65 – Rev. F; Pub. 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

49

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]