PIC32

19.0 TAP CONTROLLERS

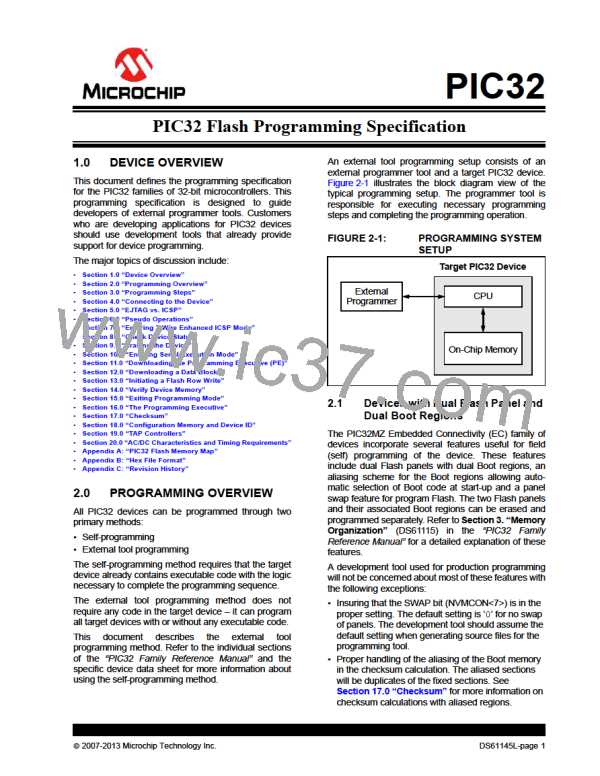

TABLE 19-1: MCHP TAP INSTRUCTIONS

Command

MTAP_COMMAND

MTAP_SW_MTAP

MTAP_SW_ETAP

MTAP_IDCODE

Value

Description

5’h0x07

5’h0x04

5’h0x05

5’h0x01

TDI and TDO connected to MCHP Command Shift register (See Table 19-2).

Switch TAP controller to MCHP TAP controller.

Switch TAP controller to EJTAG TAP controller.

Select Chip Identification Data register.

19.1.1.6

MCHP_FLASH_DISABLE

INSTRUCTION

19.1 Microchip TAP Controllers (MTAP)

19.1.1

MTAP_COMMANDINSTRUCTION

MCHP_FLASH_DISABLE clears the FAEN bit which

controls processor accesses to the Flash memory. The

FAEN bit’s state is returned in the field of the same

name. This command has no effect if CPS = 0. This

command requires a NOPto complete.

MTAP_COMMAND selects the MCHP Command Shift

register. See Table 19-2 for available commands.

19.1.1.1

MCHP_STATUSINSTRUCTION

MCHP_STATUS returns the 8-bit Status value of the

Microchip TAP controller. Table 19-3 shows the format

of the Status value returned.

Note:

This command is not required for

PIC32MZ EC family devices.

19.1.2

MTAP_SW_MTAPINSTRUCTION

19.1.1.2

MCHP_ASSERT_RSTINSTRUCTION

MTAP_SW_MTAPswitches the TAP instruction set to the

MCHP TAP instruction set.

MCHP_ASSERT_RST performs a persistent device

Reset. It is similar to asserting and holding MCLR. Its

associated Status bit is DEVRST.

19.1.3

MTAP_SW_ETAPINSTRUCTION

MTAP_SW_ETAP effectively switches the TAP

instruction set to the EJTAG TAP instruction set. It does

this by holding the EJTAG TAP controller in the Run

Test/Idle state until a MTAP_SW_ETAP instruction is

decoded by the MCHP TAP controller.

19.1.1.3

MCHP_DE_ASSERT_RST

INSTRUCTION

MCHP_DE_ASSERT_RST removes the persistent

device Reset. It is similar to de-asserting MCLR. Its

associated Status bit is DEVRST.

19.1.4

MTAP_IDCODEINSTRUCTION

19.1.1.4

MCHP_ERASEINSTRUCTION

MTAP_IDCODE returns the value stored in the DEVID

register.

MCHP_ERASE performs a Chip Erase. The CHIP_

ERASE command sets an internal bit that requests

the Flash Controller to perform the erase. Once the

controller becomes busy, as indicated by FCBUSY

(Status bit), the internal bit is cleared.

19.1.1.5

MCHP_FLASH_ENABLE

INSTRUCTION

MCHP_FLASH_ENABLE sets the FAEN bit, which con-

trols processor accesses to the Flash memory. The

FAEN bit’s state is returned in the field of the same

name. This command has no effect if CPS = 0. This

command requires a NOPto complete.

Note:

This command is not required for

PIC32MZ EC family devices.

2007-2013 Microchip Technology Inc.

DS61145L-page 55

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]