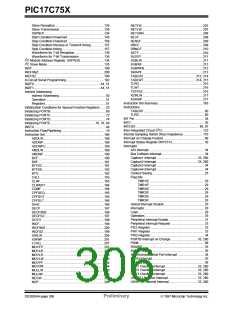

PIC17C75X

Baud Rate Formula .......................................................... 110

Baud Rate Generator ....................................................... 143

Baud Rate Generator (BRG) ............................................ 110

Baud Rates

Asynchronous Mode................................................. 112

Synchronous Mode................................................... 111

BCF .................................................................................. 190

BCLIE ..................................................................................32

BCLIF ..................................................................................34

BF............................................................. 124, 135, 149, 152

Bit Manipulation................................................................ 184

Block Diagrams

Index

A

A/D

Accuracy/Error .......................................................... 174

ADCON0 Register..................................................... 167

ADCON1 Register..................................................... 168

ADIF bit..................................................................... 169

Analog Input Model Block Diagram........................... 170

Analog-to-Digital Converter....................................... 167

Block Diagram........................................................... 169

Configuring Analog Port Pins.................................... 172

Configuring the Interrupt ........................................... 169

Configuring the Module............................................. 169

Connection Considerations....................................... 174

Conversion Clock...................................................... 171

Conversions.............................................................. 172

Converter Characteristics ......................................... 245

Delays....................................................................... 170

Effects of a Reset...................................................... 174

Equations.................................................................. 170

Flowchart of A/D Operation....................................... 175

GO/DONE bit ............................................................ 169

Internal Sampling Switch (Rss) Impedence.............. 170

Operation During Sleep ............................................ 173

Sampling Requirements............................................ 170

Sampling Time.......................................................... 170

Source Impedence.................................................... 170

Time Delays.............................................................. 170

Transfer Function...................................................... 174

A/D Interrupt........................................................................ 34

A/D Interrupt Flag bit, ADIF................................................. 34

A/D Module Interrupt Enable, ADIE .................................... 32

ACK........................................................................... 135, 268

Acknowledge Data bitr, AKD............................................. 126

Acknowledge Pulse........................................................... 135

Acknowledge Sequence Enable bit, AKE ......................... 126

Acknowledge Status bit, AKS ........................................... 126

ADCON0............................................................................. 45

ADCON1............................................................................. 45

ADDLW............................................................................. 188

ADDWF............................................................................. 188

ADDWFC .......................................................................... 189

ADIE.................................................................................... 32

ADIF.................................................................................... 34

ADRES Register ............................................................... 167

ADRESH............................................................................. 45

ADRESL.............................................................................. 45

AKD................................................................................... 126

AKE................................................................................... 126

AKS........................................................................... 126, 149

ALU....................................................................................... 9

ALUSTA...................................................................... 44, 184

ALUSTA Register................................................................ 47

ANDLW............................................................................. 189

ANDWF............................................................................. 190

Application Note AN552,"Implementing Wake-up

A/D............................................................................ 169

Analog Input Model................................................... 170

Baud Rate Generator ............................................... 143

BSR Operation ............................................................53

External Brown-out Protection Circuit (Case1)............28

External Power-on Reset Circuit .................................22

External Program Memory Connection .......................41

2

I C Master Mode ...................................................... 141

2

I C Module................................................................ 134

Indirect Addressing......................................................50

On-chip Reset Circuit ..................................................21

PORTD........................................................................74

PORTE ........................................................................76

Program Counter Operation ........................................52

PWM............................................................................97

RA0 and RA1...............................................................65

RA2..............................................................................66

RA3..............................................................................66

RA4 and RA5...............................................................66

RB3:RB2 Port Pins......................................................69

RB7:RB4 and RB1:RB0 Port Pins...............................68

RC7:RC0 Port Pins......................................................72

2

SSP (I C Mode)........................................................ 134

SSP (SPI Mode) ....................................................... 128

2

SSP Module (I C Master Mode)............................... 123

2

SSP Module (I C Slave Mode)................................. 123

SSP Module (SPI Mode) .......................................... 123

Timer3 with One Capture and One Period Register. 100

TMR1 and TMR2 in 16-bit Timer/Counter Mode .........95

TMR1 and TMR2 in Two 8-bit Timer/Counter Mode ...94

TMR3 with Two Capture Registers........................... 102

Using CALL, GOTO.....................................................52

WDT ......................................................................... 179

BODEN................................................................................28

Borrow ...................................................................................9

BRG.......................................................................... 110, 143

Brown-out Protection...........................................................28

Brown-out Reset (BOR).......................................................28

BSF................................................................................... 191

BSR .............................................................................. 44, 53

BSR Operation ....................................................................53

BTFSC.............................................................................. 191

BTFSS.............................................................................. 192

BTG .................................................................................. 192

Buffer Full bit, BF.............................................................. 135

Buffer Full Status bit, BF................................................... 124

Bus Arbitration.................................................................. 160

Bus Collision

on Keystroke"...................................................................... 68

Application Note AN578, "Use of the SSP Module in

2

the I C Multi-Master Environment."................................... 123

Assembler......................................................................... 220

Asynchronous Master Transmission................................. 114

Asynchronous Transmitter................................................ 113

Section...................................................................... 160

Bus Collision During a RESTART Condition .................... 163

Bus Collision During a Start Condition ............................. 161

Bus Collision During a Stop Condition.............................. 164

Bus Collision Interrupt Enable, BCLIE.................................32

Bus Collision Interrupt Flag bit, BCLIF ................................34

B

Bank Select Register (BSR)................................................ 53

Banking......................................................................... 42, 53

1997 Microchip Technology Inc.

Preliminary

DS30264A-page 303

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]