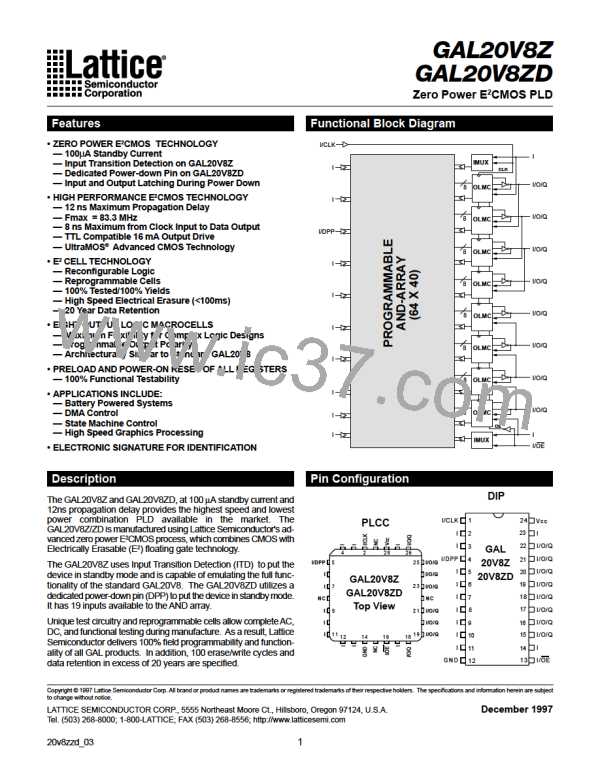

Specifications GAL20V8Z

GAL20V8ZD

Simple Mode

In the Simple mode, macrocells are configured as dedicated inputs

or as dedicated, always active, combinatorial outputs.

Pins 1(2) and 13(16) are always available as data inputs into the

AND array. The center two macrocells (pins 18(21) & 19(23)) can-

not be used in the input configuration.

Architecture configurations available in this mode are similar to the

common 14L8 and 16P6 devices with many permutations of ge-

neric output polarity or input choices.

Pin 4(5) is used as dedicated power-down pin on GAL20V8ZD. It

cannot be used as functional input.

All outputs in the simple mode have a maximum of eight product

terms that can control the logic. In addition, each output has pro-

grammable polarity.

The JEDEC fuse numbers including the UES fuses and PTD fuses

are shown on the logic diagram.

Combinatorial Output with Feedback Configuration

for Simple Mode

Vcc

- SYN=1.

- AC0=0.

- XOR=0 defines Active Low Output.

- XOR=1 defines Active High Output.

- AC1=0 defines this configuration.

- All OLMC except pins 18(21) & 19(23) can be

configured to this function.

XOR

Combinatorial Output Configuration for Simple Mode

Vcc

- SYN=1.

- AC0=0.

- XOR=0 defines Active Low Output.

- XOR=1 defines Active High Output.

- AC1=0 defines this configuration.

- Pins 18(21) & 19(23) are permanently configured to

this function.

XOR

Dedicated Input Configuration for Simple Mode

- SYN=1.

- AC0=0.

- XOR=0 defines Active Low Output.

- XOR=1 defines Active High Output.

- AC1=1 defines this configuration.

- All OLMC except pins 18(21) & 19(23) can be

configured to this function.

Note: The development software configures all of the architecture control bits and checks for proper pin usage automatically.

8

LATTICE [ LATTICE SEMICONDUCTOR ]

LATTICE [ LATTICE SEMICONDUCTOR ]